Оглавление:

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 11:51.

- Последнее изменение 2025-01-23 15:05.

В этом руководстве обсуждается создание простого мастера I2C на VHDL.

ПРИМЕЧАНИЕ: щелкните каждое изображение, чтобы увидеть полное изображение

Шаг 1. Обзор шины I2C

• Стенды для Inter Integrated Circuit.

• Синхронный, полудуплексный.

• Двухпроводный интерфейс - SDA и SCL.

• SDA - Последовательная линия данных, управляемая ведущим и ведомым

• SCL - последовательные часы, генерируемые мастером

• Протокол с несколькими ведущими и ведомыми устройствами.

• Два режима - 100 кбит / с и 400 кбит / с: медленный и быстрый.

Шаг 2: Дизайн RTL на VHDL

Технические характеристики нашего мастера I2C

- 8-битный фрейм данных.

- Только однонаправленное управление SCL.

- 7-битный адрес ведомого устройства.

- Поддерживает как медленный, так и быстрый режимы.

- Один мастер, несколько подчиненных.

- Соответствует оригинальным спецификациям I2C от Philips.

Используется чистый код RTL. Таким образом, IP легко переносится на все FPGA. Компактная конструкция на основе конечных автоматов с внутренне генерируемыми часами обеспечивает оптимальную площадь и производительность.

Шаг 3: моделирование и тестирование

Тестовая среда

- Функциональное моделирование и тестирование с использованием стороннего I2C Slave IP.

- Синтезирован с использованием набора инструментов Xilinx Vivado.

- Реализовано и протестировано на плате ПЛИС Artix-7.

- По таймингу проверенная конструкция на 100 МГц.

- Проверенные формы сигналов на DSO / CRO.

- Успешно протестирована связь с Arduino UNO в качестве ведомого устройства I2C.

Шаг 4: важные примечания

- При тестировании ведущего устройства с использованием IP-адреса ведомого устройства I2C настройте код ведомого устройства в соответствии с вашими требованиями. Вы можете изменить тактовую частоту по умолчанию и адрес ведомого устройства. Тактовая частота также должна быть настроена в Мастер-коде.

- При тестировании на плате не забывайте подтягивающие резисторы, так как линия SDA является общим стоком !!! Поищите в Google рекомендуемые подтягивающие резисторы для различных скоростей i2c. Я использовал 2.2K для 100 кГц.

- Если вы не используете испытательный стенд и моделируете Мастер независимо, тщательно моделируйте сигнал SDA, так как это двунаправленный сигнал (входящий) сигнал. Он имеет два драйвера, ведущую и ведомую. Вы должны знать, когда «принуждать», а когда «отменять».

- SCL - однонаправленная линия. Нет необходимости подтягиваться.

- Пожалуйста, внимательно ознакомьтесь с IP-документацией.

Шаг 5: прикрепленные файлы

- Все коды RTL I2C Master.

- Тестовый стенд, а также коды I2C Slave для тестирования.

- Документация по ИС.

По любым вопросам обращайтесь ко мне:

Миту Радж

следуй за мной:

По вопросам обращайтесь: iammituraj@gmail.com

Рекомендуемые:

Дизайн игры в Flick за 5 шагов: 5 шагов

Дизайн игры в Flick за 5 шагов: Flick - это действительно простой способ создания игры, особенно чего-то вроде головоломки, визуального романа или приключенческой игры

UX-дизайн почтового бота: 6 шагов

Mail Bot UX Design: это робот, который кричит на вас, когда у вас есть почта. Вам нужен клей и скотч

Дизайн SPI Master на VHDL: 6 шагов

Дизайн мастера шины SPI на VHDL: в этом руководстве мы собираемся разработать мастер шины SPI с нуля на VHDL

Дизайн UART на VHDL: 5 шагов

Дизайн UART на VHDL: UART означает универсальный асинхронный приемный передатчик. Это самый популярный и простой протокол последовательной связи. В этом руководстве вы узнаете, как создать модуль UART на VHDL

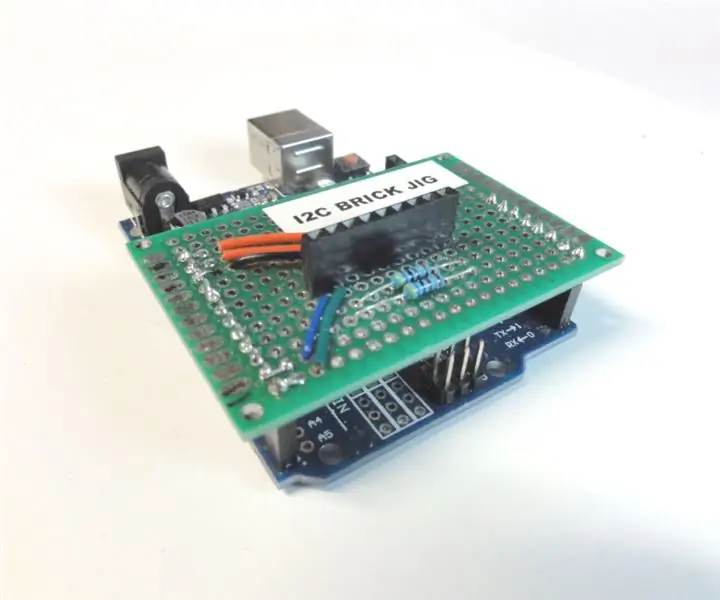

IOT123 - I2C BRICK MASTER JIG: 4 шага

IOT123 - I2C BRICK MASTER JIG: При разработке ASSIMILATE SENSORS и ACTORS я держу UNO под рукой для отправки adhoc-команд I2C разрабатываемым прототипам. Одним из преимуществ I2C BRICKS является стандартизированная распиновка. Вместо того, чтобы каждый раз использовать макетные провода