Оглавление:

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 11:51.

- Последнее изменение 2025-01-23 15:05.

В этом руководстве мы собираемся разработать мастер шины SPI с нуля на VHDL.

Шаг 1. Обзор SPI

- SPI - это синхронная последовательная шина

- Его популярность и простота сделали его фактическим стандартом в последовательной связи.

- Полнодуплексный автобус

- Простой протокол и одна из самых быстрых последовательных шин

Шаг 2: Технические характеристики конструкции

Вот характеристики SPI Master, которые мы собираемся разработать:

- Поддерживает все четыре режима работы; динамически настраиваемый

- Контроль включения часов для экономии энергии

- Статически настраиваемая длина слова и скорость

- Единое прерывание как для передачи, так и для приема

Шаг 3. Начало работы

Во-первых, у нашего IP должно быть два интерфейса. Один - это последовательный интерфейс, а другой - параллельный интерфейс. Последовательный интерфейс состоит из де-факто стандартных сигналов SPI: MOSI, MISO, SS, SCLK.

MOSI иногда называют SDO, а MISO иногда называют SDI.

Последовательный интерфейс используется для связи с внешними периферийными устройствами, т. Е. С ведомыми устройствами SPI.

Параллельный интерфейс используется для связи с нашим хостом, то есть с микроконтроллером или микропроцессором, который фактически сообщает Мастеру, какие данные должны быть последовательно переданы и получены по последовательным линиям. т.е. все шины данных принадлежат параллельному интерфейсу.

У нас есть глобальные часы, которые управляют внутренней логикой SPI, а также SCLK, который мы генерируем внутри.

У нас также есть некоторые управляющие сигналы, такие как разрешение записи, разрешение часов. И прерывание, и другие статусные сигналы.

Поскольку нам приходится иметь дело со сложными условиями управления, проще спроектировать такие IP-адреса для последовательной связи, как конечный автомат. Мы также спроектируем мастер SPI как конечный автомат. FSM будет управляться другими внутренними часами, которые в два раза больше SCLK. Эти внутренние часы генерируются с использованием синхронных счетчиков глобальных часов.

Все управляющие сигналы, которые пересекают тактовые домены, имеют синхронизаторы для большей безопасности.

Шаг 4: RTL-представление главного ядра SPI и сигналов моделирования

Это простая конструкция RTL без использования выделенных IP-адресов FPGA. Следовательно, это полностью переносимый код для любой FPGA.

Рекомендуемые:

Дизайн игры в Flick за 5 шагов: 5 шагов

Дизайн игры в Flick за 5 шагов: Flick - это действительно простой способ создания игры, особенно чего-то вроде головоломки, визуального романа или приключенческой игры

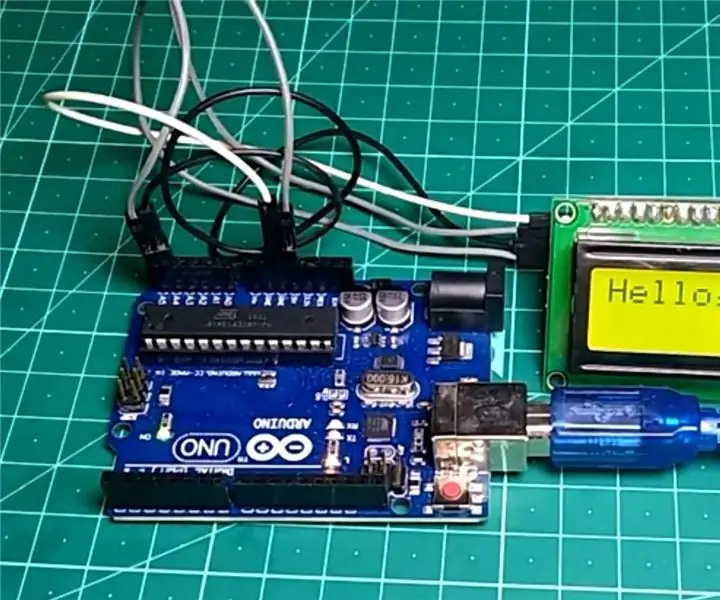

ЖК-дисплей I2C / IIC - Использование ЖК-дисплея SPI для ЖК-дисплея I2C Использование модуля SPI-IIC с Arduino: 5 шагов

ЖК-дисплей I2C / IIC | Используйте ЖК-дисплей SPI для ЖК-дисплея I2C Использование модуля SPI-IIC с Arduino: Привет, ребята, так как обычный ЖК-дисплей SPI 1602 имеет слишком много проводов для подключения, поэтому его очень сложно связать с Arduino, но на рынке доступен один модуль, который может преобразовать дисплей SPI в дисплей IIC, поэтому вам нужно подключить только 4 провода

Дизайн I2C Master на VHDL: 5 шагов

Дизайн мастера I2C на VHDL: в этой инструкции обсуждается создание простого мастера I2C на VHDL. ПРИМЕЧАНИЕ: щелкните каждое изображение, чтобы увидеть полное изображение

Дизайн UART на VHDL: 5 шагов

Дизайн UART на VHDL: UART означает универсальный асинхронный приемный передатчик. Это самый популярный и простой протокол последовательной связи. В этом руководстве вы узнаете, как создать модуль UART на VHDL

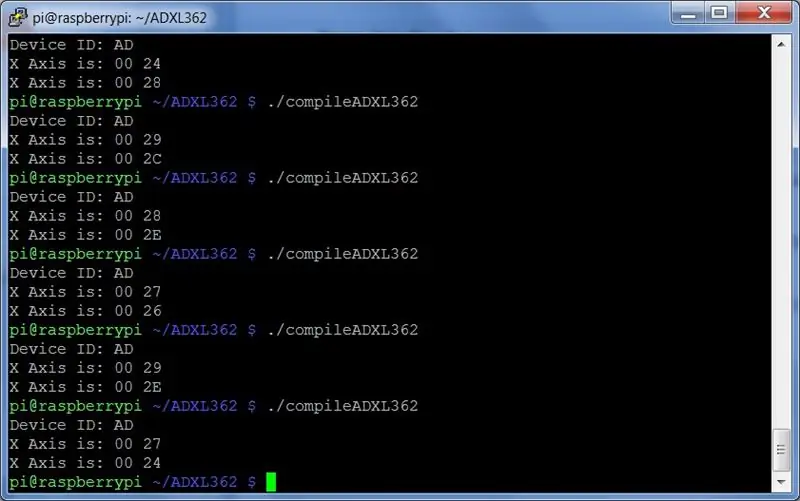

Предварительный * SPI на Pi: обмен данными с 3-осевым акселерометром SPI с использованием Raspberry Pi: 10 шагов

Предварительный * SPI на Pi: Связь с 3-осевым акселерометром SPI с использованием Raspberry Pi: Пошаговое руководство по настройке Raspbian и взаимодействию с устройством SPI с использованием библиотеки SPI bcm2835 (НЕ битый!) очень предварительный … Мне нужно добавить более качественные фотографии физического подключения и проработать некоторый неудобный код