Оглавление:

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 11:50.

- Последнее изменение 2025-01-23 15:04.

Подключите плату разработки Mojo к внешним входам с помощью этого экрана.

Что такое плата разработки Mojo?

Плата для разработки Mojo - это плата для разработки, основанная на ПЛИС Xilinx spartan 3. Плата изготовлена компанией Alchitry. FPGA очень полезны, когда несколько процессов должны выполняться одновременно.

Что вам понадобится?

Запасы

Доска разработки Mojo

Файл Гербера

8 резисторов по 15 кОм (опционально *)

4 резистора по 470 Ом

4 резистора по 560 Ом

4 семисегментных дисплея CC

4 х 3 мм светодиода

4 тактильных переключателя SPDT

1 x 4-позиционный DIP-переключатель для поверхностного монтажа

2 x 25 на 2 или 4 x 25 заголовков

1x 2х5-контактная головка коробки

Паяльник

Припой

Поток

* (если эти резисторы не установлены, для соответствующих выводов должен быть включен внутренний подтягивающий / понижающий ток)

Шаг 1. Загрузите Gerber на производителя печатных плат по вашему выбору

Для своих плат я заказал у JLC PCB.

Единственное изменение, которое я сделал, - это цвет, который я хотел соответствовать черному цвету Mojo.

Шаг 2: Сборка платы

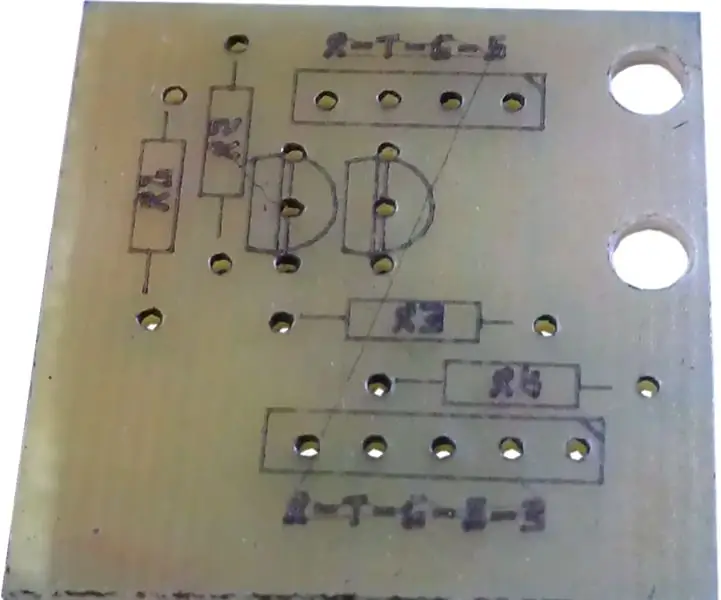

При пайке я всегда считаю полезным сначала припаять самые нижние части, поэтому начать с резисторов - хорошая идея.

R5, R6, R7, R8, R9, R10, R11 и R12 - резисторы на 15 кОм, используемые для понижения переключателей (если вы используете внутреннее подтягивание / подтягивание, игнорируйте это).

R1, R2, R3, R4 - резисторы на 560 Ом, которые отвечают за ограничение тока через 7-сегментный дисплей.

R13, R14, R15, R16 - резисторы на 470 Ом, которые отвечают за ограничение тока через 4 светодиода.

Затем припаяйте DIP-переключатель, тактильные переключатели, светодиоды, семисегментные дисплеи и разъем заголовка коробки в указанном порядке.

Теперь поместите 25 на 2 (или 2 25 на 1) в моджо, чтобы выровнять штифты. Совместите экран со штырями и припаяйте его на место.

Шаг 3: установка программного обеспечения

Для программного обеспечения, обращающегося к веб-сайту Alchitry, вы узнаете, что вам нужно, чтобы начать работу и установить Xilinx ISE. Однако изменение файла.ucf, чтобы он знал, какие контакты подключены, что важно для запуска вашей программы.

Вот файл.ucf, который я использую с щитом:

КОНФИГУРАЦИЯ VCCAUX = 3.3;

NET "clk" TNM_NET = clk; TIMESPEC TS_clk = ПЕРИОД "clk" 50 МГц ВЫСОКИЙ 50%; NET "clk" LOC = P56 | IOSTANDARD = LVTTL; NET "rst_n" LOC = P38 | IOSTANDARD = LVTTL; NET "cclk" LOC = P70 | IOSTANDARD = LVTTL; NET "spi_mosi" LOC = P44 | IOSTANDARD = LVTTL; NET "spi_miso" LOC = P45 | IOSTANDARD = LVTTL; NET "spi_ss" LOC = P48 | IOSTANDARD = LVTTL; NET "spi_sck" LOC = P43 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDARD = LVTTL; NET "avr_tx" LOC = P55 | IOSTANDARD = LVTTL; NET "avr_rx" LOC = P59 | IOSTANDARD = LVTTL; NET "avr_rx_busy" LOC = P39 | IOSTANDARD = LVTTL; NET "Q [0]" LOC = P26 | IOSTANDARD = LVTTL; NET "Q [1]" LOC = P23 | IOSTANDARD = LVTTL; NET "Q [2]" LOC = P21 | IOSTANDARD = LVTTL; NET "Q [3]" LOC = P16 | IOSTANDARD = LVTTL; NET "S [0]" LOC = P7 | IOSTANDARD = LVTTL; NET "S [1]" LOC = P9 | IOSTANDARD = LVTTL; NET "S [2]" LOC = P11 | IOSTANDARD = LVTTL; NET "S [3]" LOC = P14 | IOSTANDARD = LVTTL; NET "pb [1]" LOC = P30 | IOSTANDARD = LVTTL; NET "pb [2]" LOC = P27 | IOSTANDARD = LVTTL; NET "pb [3]" LOC = P24 | IOSTANDARD = LVTTL; NET "pb [4]" LOC = P22 | IOSTANDARD = LVTTL; NET "севсега [0]" LOC = P57 | IOSTANDARD = LVTTL; NET "sevsegb [0]" LOC = P58 | IOSTANDARD = LVTTL; NET "sevsegc [0]" LOC = P66 | IOSTANDARD = LVTTL; NET "sevsegd [0]" LOC = P67 | IOSTANDARD = LVTTL; NET "sevsege [0]" LOC = P74 | IOSTANDARD = LVTTL; NET "sevsegf [0]" LOC = P75 | IOSTANDARD = LVTTL; NET "sevsegg [0]" LOC = P78 | IOSTANDARD = LVTTL; NET "sevsegdp [0]" LOC = P80 | IOSTANDARD = LVTTL; NET "севсега [1]" LOC = P82 | IOSTANDARD = LVTTL; NET "sevsegb [1]" LOC = P83 | IOSTANDARD = LVTTL; NET "sevsegc [1]" LOC = P84 | IOSTANDARD = LVTTL; NET "sevsegd [1]" LOC = P85 | IOSTANDARD = LVTTL; NET "севсеге [1]" LOC = P87 | IOSTANDARD = LVTTL; NET "sevsegf [1]" LOC = P88 | IOSTANDARD = LVTTL; NET "sevsegg [1]" LOC = P92 | IOSTANDARD = LVTTL; NET "sevsegdp [1]" LOC = P94 | IOSTANDARD = LVTTL; NET "севсега [2]" LOC = P97 | IOSTANDARD = LVTTL; NET "sevsegb [2]" LOC = P98 | IOSTANDARD = LVTTL; NET "sevsegc [2]" LOC = P99 | IOSTANDARD = LVTTL; NET "sevsegd [2]" LOC = P100 | IOSTANDARD = LVTTL; NET "севсеге [2]" LOC = P101 | IOSTANDARD = LVTTL; NET "sevsegf [2]" LOC = P102 | IOSTANDARD = LVTTL; NET "sevsegg [2]" LOC = P104 | IOSTANDARD = LVTTL; NET "sevsegdp [2]" LOC = P111 | IOSTANDARD = LVTTL; NET "севсега [3]" LOC = P114 | IOSTANDARD = LVTTL; NET "sevsegb [3]" LOC = P115 | IOSTANDARD = LVTTL; NET "sevsegc [3]" LOC = P116 | IOSTANDARD = LVTTL; NET "sevsegd [3]" LOC = P117 | IOSTANDARD = LVTTL; NET "севсеге [3]" LOC = P118 | IOSTANDARD = LVTTL; NET "sevsegf [3]" LOC = P119 | IOSTANDARD = LVTTL; NET "sevsegg [3]" LOC = P1120 | IOSTANDARD = LVTTL; NET "sevsegdp [3]" LOC = P121 | IOSTANDARD = LVTTL;

Помните, что если вы не установили резисторы с понижающим сопротивлением, отредактируйте контакты в.ucf с помощью

| ТЯНУТЬ ВНИЗ; о

| ОСТАНОВИТЬ;

Если вы хотите использовать блок для чего-либо, соединения будут следующими. Слева - номер пина блока, а справа - пин-код mojo, который вы должны назначить в вашем.ucf:

вывод 1 = 29

вывод 2 = 51

вывод 3 = 32

вывод 4 = 41

вывод 5 = 34

вывод 6 = 35

вывод 7 = 40

вывод 8 = 33

контакт 9 = GND

вывод 10 = + V

Рекомендуемые:

Печатная плата Тима (печатная плата): 54 шага (с изображениями)

Печатная плата Тима (Plotted Circuit Board): это процесс, который я использую для создания пользовательской печатной платы для своих проектов. Чтобы сделать это: я использую свой XY Plotter с Scribe, чтобы удалить пленку для травления, чтобы обнажить медь для травителя. . Я использую свой XY-плоттер с лазером, чтобы выжигать чернила на

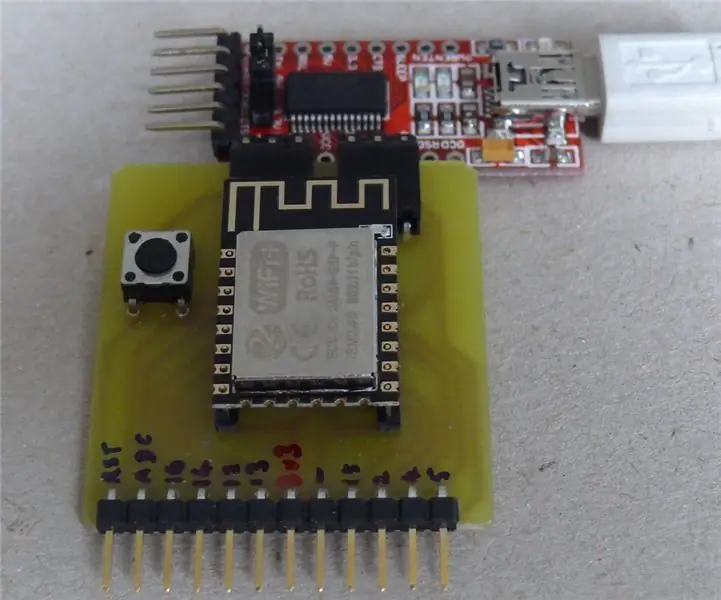

Плата для программирования и разработки ESP-12E и ESP-12F: 3 шага (с изображениями)

Плата для программирования и разработки ESP-12E и ESP-12F: Задача этой платы была простой: уметь программировать модули ESP-12E и ESP-12F так же легко, как и платы NodeMCU (т.е. не нужно нажимать кнопки). Иметь удобные для макетной платы контакты с доступом к используемому вводу-выводу. Используйте отдельный USB для последовательного конв

UDuino: очень недорогая плата для разработки, совместимая с Arduino: 7 шагов (с изображениями)

UDuino: очень дешевая плата разработки, совместимая с Arduino: платы Arduino отлично подходят для создания прототипов. Однако они становятся довольно дорогими, если у вас есть несколько параллельных проектов или вам нужно много плат контроллеров для более крупного проекта. Есть отличные и более дешевые альтернативы (Boarduino, Freeduino), но

Плата для разработки Atmega16 / 32 с ЖК-дисплеем: 8 шагов

Плата для разработки Atmega16 / 32 с ЖК-дисплеем: в этой инструкции показано, как создать собственную плату для разработки для процессоров Atmega16 или Atmega32. В Интернете полно самодельных плат для разработки, но я думаю, что есть место для другой. Эта доска была очень полезна в моем проекте

18-контактная плата разработки PIC: 3 шага

18-контактная плата для разработки PIC: Я давно играю с микросхемами PIC, но всегда обходился без какой-либо платы для разработки. С этой целью я разработал базовую доску, для которой надеялся получить какие-то материалы. Я еще не сделал эту доску, так как жду ки