Оглавление:

- Шаг 1: блок-схема

- Шаг 2: Принцип работы

- Шаг 3: реализация логики

- Шаг 4: разрешение тупиковой ситуации

- Шаг 5: Конфигурация устройства - схема Matrix0

- Шаг 6: Конфигурация устройства - логика синхронизации SPI

- Шаг 7. Конфигурация устройства - свойства компонентов Matrix0

- Шаг 8: Конфигурация устройства - схема Matrix1

- Шаг 9: Конфигурация устройства - 3-битный двоичный счетчик

- Шаг 10: Конфигурация устройства - 3-битная логика сравнения

- Шаг 11: Конфигурация устройства - логика цифрового сравнения и временный регистр

- Шаг 12: Конфигурация устройства - Свойства компонентов Matrix1

- Шаг 13: результаты

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 11:49.

- Последнее изменение 2025-01-23 15:04.

Системы управления и связанные устройства имеют дело с несколькими источниками питания, такими как линии смещения или батареи, и должны отслеживать самую высокую (или самую низкую) линию среди данного набора.

Например, переключение нагрузки в системе с питанием от «нескольких батарей» требует, чтобы система отслеживала минимальное или максимальное напряжение в группе батарей (максимальное или минимальное в зависимости от конкретного алгоритма переключения) и динамически направляла нагрузку на наиболее подходящий источник в реальном времени. В качестве альтернативы системе может потребоваться временно отключить аккумулятор с самым низким напряжением для правильной зарядки.

Другой пример - современная солнечная энергетическая система, где каждая солнечная панель оснащена механизмом поворота и наклона и схемой слежения за солнечным светом (последняя предоставляет информацию о положении Солнца для ориентации панели). Имея информацию о максимальном напряжении, можно точно настроить положение каждой солнечной панели в зависимости от того, действительно ли панель гирлянды обеспечивает самое высокое выходное напряжение, тем самым достигая превосходного уровня оптимизации мощности.

Есть несколько различных марок коммерческих ИС (в основном микроконтроллеры), которые в принципе могут реализовать повторитель максимального напряжения. Однако они требуют программирования и менее рентабельны, чем решения для смешанных сигналов. Дополнение конструкции Dialog GreenPAKTM может положительно повлиять на доступность, размер и модульность конструкции. Эта конструкция использует преимущество интеграции как аналоговой, так и цифровой схемы в одну микросхему.

В этой инструкции реализованы аналоговый интерфейс и цифровая логика, необходимые для реализации определения максимального (или, возможно, минимального) напряжения среди восьми различных источников.

Для реализации 8-канального аналогового монитора максимального / минимального напряжения используется SLG46620G.

Ниже мы описали шаги, необходимые для понимания того, как было запрограммировано решение для создания 8-канального аналогового монитора максимального / минимального напряжения. Однако, если вы просто хотите получить результат программирования, загрузите программное обеспечение GreenPAK, чтобы просмотреть уже заполненный файл дизайна GreenPAK. Подключите GreenPAK Development Kit к компьютеру и запустите программу для создания 8-канального аналогового монитора максимального / минимального напряжения.

Шаг 1: блок-схема

На рисунке 1 представлена глобальная диаграмма реализованной системы.

Линия до 8 источников переменного напряжения мультиплексируется и подключается к модулю АЦП GreenPAK, подключенному к индивидуальной внутренней конструкции, способной выбирать источник с наивысшим напряжением по сравнению с другими. Внутренняя логика выводит эту информацию для отображения или дальнейшей обработки.

Дизайн основан на продукте GreenPAK SLG46620G, поскольку он включает в себя все необходимые аналоговые и цифровые строительные блоки для приложения. В этой реализации массив сканируется с помощью аналогового мультиплексора ADG508, который напрямую управляется ИС GreenPAK.

Выходная информация представляет собой 3-битное цифровое число, соответствующее номеру источника напряжения при максимальном напряжении. Прямой способ получить эту информацию - отобразить номер на 7-сегментном дисплее. Это может быть легко выполнено путем сопряжения цифрового выхода SLG46620G с 7-сегментным драйвером дисплея, таким как решение GreenPAK, описанное в Справочнике, или с общей микросхемой 74LS47.

Представленная схема рассчитана на максимальное напряжение. Чтобы преобразовать конструкцию в устройство для определения минимального напряжения, необходимо добавить простую схему предварительного согласования между аналоговым мультиплексором и аналоговым входом GreenPAK, вычитая выход мультиплексора из опорного напряжения 1 В.

Шаг 2: Принцип работы

Дизайн направлен на выбор источника с максимальным напряжением, поэтому сканирование выполняется по всему массиву, сохраняя последнее максимальное значение и сравнивая его со следующим значением на входе (которое принадлежит следующему источнику напряжения в сканировании).

Далее мы будем называть полную последовательность мультиплексирования по всем входам «сканированием» или «петлей».

Сравнение двух значений выполняется не с помощью компонентов ACMP (однако, доступных в SLG46620G), а с помощью модуля DCMP после того, как значения соответственно оцифрованы. Это продвинутый и усовершенствованный метод, впервые рассматриваемый в Справочнике.

На рисунке 2 показано, как SLG46620G устроен для этой конструкции.

Аналоговый входной сигнал поступает на вход АЦП через компонент PGA с установленным усилением 1. Также возможны различные настройки усиления, чтобы найти наилучшее совпадение с входной электроникой согласования, предназначенной для отображения входных напряжений на 0-1 В. ассортимент модуля АЦП GreenPAK.

АЦП работает в несимметричном режиме и преобразует аналоговый сигнал в 8-битный цифровой код, который затем передается в модуль DCMP. Цифровой код также подается в блок SPI, сконфигурированный как буфер ADC / FSM, где цифровой код может быть сохранен и не изменится, пока следующий импульс не поступит на вход SPI CLK. Обратите внимание, что специальный логический блок управляет входом SPI CLK. Мы рассмотрим эту часть позже, так как это «основная» логика, отвечающая за правильную работу. Новый цифровой код сохраняется в модуле SPI только в том случае, если он принадлежит фактическому максимальному входному напряжению.

Компонент DCMP используется для сравнения текущих данных АЦП с последним победителем (то есть последним найденным максимумом), который хранится в блоке SPI. Он будет генерировать импульс на выходе OUT +, когда новые данные АЦП больше, чем предыдущие. Мы используем сигнал OUT +, чтобы обновить блок SPI с новым победителем.

Глобальный тактовый сигнал управляет преобразованиями АЦП и общими таймингами. Как только преобразование выполнено, выходной сигнал INT АЦП подает импульсы, согласованные по времени с параллельным выводом данных АЦП. Мы также используем выход INT для увеличения 3-битного двоичного счетчика, реализованного DFF в Matrix1, что полезно по трем причинам:

1. Выходные линии счетчика обращаются к внешнему аналоговому мультиплексору, таким образом подавая следующее входное напряжение на АЦП;

2. Счетчик фиксируется в 3-битном регистре (реализованном в Matrix1) для сохранения временного победителя во время сканирования;

3. Счетчик декодируется для обновления второго 3-битного регистра (реализованного в Matrix0) после завершения сканирования.

Шаг 3: реализация логики

Модуль АЦП последовательно предоставляет преобразованные данные всех входных напряжений, одно за другим, на неопределенный срок. Как только мультиплексор адресуется 0b111 (десятичное 7), счетчик скатывается до 0b000 (десятичный 0), таким образом, начинается новое сканирование входных напряжений.

Во время сканирования выходной сигнал ADC INT генерируется, когда параллельный вывод данных является допустимым. Когда этот сигнал пульсирует, аналоговый мультиплексор должен переключиться на следующий вход, обеспечивая PGA соответствующим напряжением. Следовательно, выход ADC INT является прямым синхронизирующим сигналом 3-битного двоичного счетчика на Рисунке 2, чье 3-битное параллельное выходное слово напрямую обращается к внешнему аналоговому мультиплексору («V select» на Рисунке 1).

Давайте теперь обратимся к примеру, где предполагается, что входные напряжения имеют следующие отношения:

а) V0 <V1 <V2

б) V2> V3, V4

в) V5> V2

На рисунке 3 представлены основные сигналы, задействованные в механизме принятия максимального решения.

Поскольку данные в конечном итоге синхронизируются в буферный регистр SPI синхронно с импульсами INT, существует окно сравнения, в котором содержимое буфера SPI сравнивается со следующим результатом преобразования АЦП. Эта конкретная синхронизация приводит к генерации импульсов OUT + на выходе DCMP. Мы можем использовать эти импульсы для загрузки новых значений в буферный регистр SPI.

Как видно из строки данных буфера SPI на предыдущем рисунке, регистр SPI всегда содержит, время от времени, наибольшее значение среди 8 входов, и он обновляется только тогда, когда большее значение обнаруживается модулем DCMP (имеется в виду DCMP Выходная линия OUT + графика, пропущенные импульсы заставляют V2 оставаться зафиксированным в регистре до тех пор, пока он не сравнится с V5).

Шаг 4: разрешение тупиковой ситуации

Если бы реализованная логика была бы такой, как описано выше, ясно, что мы столкнемся с ситуацией взаимоблокировки: система способна обнаруживать только напряжения выше, чем то, которое соответствует тому, что хранится в буферном регистре SPI.

Это также справедливо в случае, если это напряжение уменьшится, а затем другой вход, который до сих пор был ниже этого, становится самым высоким: он никогда не будет обнаружен. Эту ситуацию лучше объяснить на Рисунке 4, где присутствуют только 3 входных напряжения. ясность.

Во время итерации 2 V3 падает, и V1 - это фактическое максимальное напряжение. Но модуль DCMP не выдает импульс, потому что данные, хранящиеся в буферном регистре SPI (соответствующие 0,6 В), больше, чем данные, соответствующие V1 (0,4 В).

Затем система ведет себя как «абсолютный» искатель максимума и некорректно обновляет вывод.

Хороший способ решить эту проблему - принудительно перезагрузить данные в буферный регистр SPI, когда система завершит полный цикл опроса всех каналов.

Фактически, если напряжение на этом входе все еще самое высокое, ничего не меняется, и управление безопасно продолжается (как показано на Рисунке 4 выше, это случай циклических итераций 0 и 1). С другой стороны, если напряжение на этом входе случайно падает до значения, меньшего, чем на другом входе, то перезагрузка значения дает возможность модулю DCMP создать импульс OUT + при сравнении его с новым максимальным значением (это случай итераций цикла 2 и 3).

Чтобы решить эту проблему, необходима логическая схема. Он должен генерировать тактовый сигнал для компонента SPI, когда цикл достигает фактического максимального входного значения, тем самым вызывая повторную загрузку своего обновленного слова данных в буферный регистр SPI. Это будет обсуждаться в разделах 7.2 и 7.6 ниже.

Шаг 5: Конфигурация устройства - схема Matrix0

SLG46620G имеет два блока Matrix, как показано на рисунке 2. На следующих рисунках показаны соответствующие конфигурации устройств.

Верхняя часть схемы - это «регистр цикла», реализованный с 3 DFF (DFF0, DFF1 и DFF2). Он обновляется после каждого цикла входного мультиплексора для отправки 7-сегментному драйверу дисплея двоичного числа «победителя», то есть входа с самым высоким напряжением в последнем сканировании. Как часы для DFF, так и данные поступают от логики, реализованной в Matrix1, через порт P12, P13, P14 и P15 соответственно.

Нижняя часть - это аналоговый интерфейс с входом на выводе 8 и PGA с усилением x1. Выход ADC INT поступает как на логику синхронизации SPI, так и на Matrix1 через порт P0, где он будет служить тактовым сигналом для реализованного счетчика.

Параллельные выходы данных ADC и SPI обозначены соответственно NET11 и NET15 и должны быть подключены к компоненту DCMP в Matrix1.

Шаг 6: Конфигурация устройства - логика синхронизации SPI

Как указывалось ранее в разделе «Логическая реализация», буферный регистр SPI обновляется каждый раз, когда сравнение между фактическим сохраненным значением и новыми данными преобразования АЦП генерирует импульс на выходе DCMP OUT +.

Целостность сигнала гарантируется, если этот сигнал объединяется с выходом ADC INT. Это позволяет избежать всплесков и ложных срабатываний.

Мы также подчеркнули, что для того, чтобы пропустить ситуации взаимоблокировки, буфер SPI должен обновляться, когда цикл достигает фактических данных победителя.

В этом случае для правильной синхронизации SPI используются три сигнала:

1. Выход ADC INT (LUT0-IN1)

2. DCMP OUT + выход (LUT0-IN0 через порт P10)

3. Счетчик равен сигналу защелки (LUT0-IN2 через порт P11)

Первые два объединены И и оба ИЛИ с последним в LUT0, реализация которого сконфигурирована, как на рисунке 6.

Шаг 7. Конфигурация устройства - свойства компонентов Matrix0

На рисунках 7-10 показаны остальные окна свойств компонентов, принадлежащие Matrix0.

Шаг 8: Конфигурация устройства - схема Matrix1

Шаг 9: Конфигурация устройства - 3-битный двоичный счетчик

Верхняя часть схемы содержит логические элементы, в основном 3-битный двоичный счетчик, синхронизируемый выходом ADC INT, как уже обсуждалось. Этот счетчик реализован по вполне «стандартной» схеме, показанной на рисунке 12.

Этот счетчик реализован в нашей конструкции с помощью триггеров DFF9, DFF10, DFF11 и INV1, LUT4, LUT8. Выход DFF9 - это LSB, а DFF11 - это MSB, как показано на рисунке 13.

LUT4 настроен как XOR, в то время как LUT8 выполняет логику AND-XOR, показанную на рисунке 12.

Выходы счетчика идут на три цифровых выходных контакта для адресации внешнего аналогового мультиплексора.

LUT10 декодирует код счетчика, когда сканирование завершено, и подает импульс в Matrix0 через DLY8 и порт P12. Это просто выполняется операцией И с выходами счетчика, таким образом декодируя число 7 dec (двоичное значение 0b111, конец цикла).

Шаг 10: Конфигурация устройства - 3-битная логика сравнения

На рисунке 15 показана схема, используемая для обнаружения повторения цикла по текущему адресу «победителя». В этом случае, как уже обсуждалось, цифровой импульс должен вызвать повторную загрузку текущего результата АЦП, чтобы разрешить возможную тупиковую ситуацию.

Адрес «победителя» сохраняется во временном регистре Matrix1 (см. Ниже), а текущий адрес выводится двоичным счетчиком.

Элементы XNOR обеспечивают истинный (логическая 1 или «высокий») выход, когда оба входа равны. И-операция этого сигнала для всех битов (LUT9) дает нам импульс, когда оба двоичных кода одинаковы. Подробности о вентилях XOR в качестве средства проверки четности можно найти в Справочнике.

Сигнал «Counter-Equals-Latch» передается в Matrix0 через порт P11.

Шаг 11: Конфигурация устройства - логика цифрового сравнения и временный регистр

В нижней части рисунка 11 (выделенного на рисунке 16) показан блок DCMP, часть этого проекта, отвечающая за принятие решений.

DFF6, 7 и 8 образуют 3-битный регистр для хранения временного входного числа «победитель» во время выполнения цикла. Входными данными для триггеров являются выходы 3-битных двоичных счетчиков, как видно в глобальной схеме Matrix1 на рисунке 11, здесь для ясности пропущено.

Выходы этого регистра не могут напрямую управлять 7-сегментным дисплеем, потому что хранимое здесь значение изменяется во время сканирования и должно считаться «действительным» только в конце самого сканирования.

По этой причине выходы временных регистров подключаются к циклическому регистру Matrix0 через межматричные порты P13, P14 и P15.

На рисунке 16 важно заметить, что временный регистр синхронизируется выходом DCMP OUT +, когда сравнение регистров ADC-SPI приводит к обнаружению нового максимума.

Тот же сигнал OUT + передается в Matrix0, SPI CLK Logic, через порт P10.

Шаг 12: Конфигурация устройства - Свойства компонентов Matrix1

На рисунках 17-19 показаны окна свойств компонентов, принадлежащие Matrix1.

Шаг 13: результаты

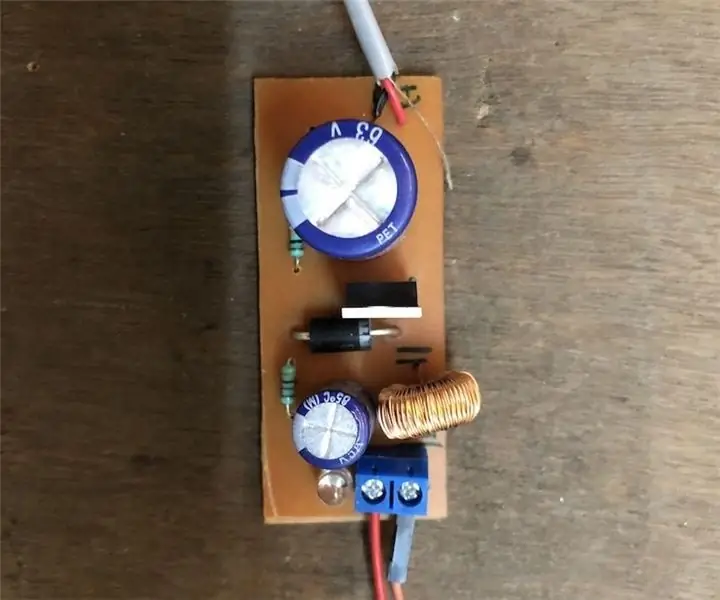

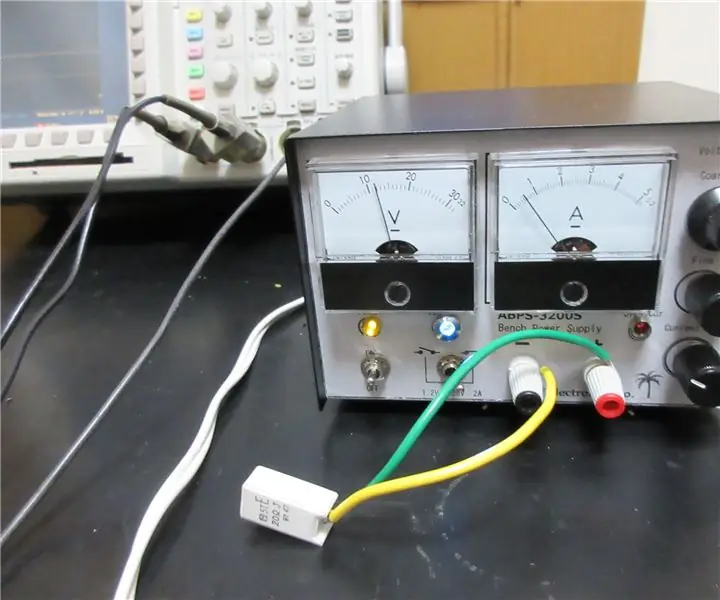

Для тестирования реализации был построен прототип оценочной платы, где 8 аналоговых входных напряжений получены с помощью ряда резисторных делителей с TrimPots (как показано на рисунке 20).

Используемый мультиплексор представляет собой ADG508, часть, которая может работать от однополярного питания (12 В).

Драйвер 7-сегментного дисплея - 74LS47. Он декодирует параллельное входное слово и напрямую управляет 7-сегментным дисплеем с общим анодом.

Оценочная плата имеет угловой разъем 2x10 для подключения непосредственно к расширенной платформе разработки GreenPAK через разъем расширения, как показано на рисунке 21.

В сочетании с усовершенствованной платформой разработки GreenPAK очень просто выполнять измерения сигналов для быстрой проверки. Например, на рис. 22 показан набор сигналов (соответственно ЧАСЫ, выход ADC INT и выход DCMP OUT +), захваченных логическим анализатором HP 54620A. Формы сигнала запускаются нарастающим фронтом сигнала OUT + (на осциллографе, помеченном как «A> B»), следовательно, это захват формы сигнала, когда новое максимальное напряжение обнаруживается среди аналоговых входов. Фактически, это было получено путем вращения одного из подстроечных резисторов оценочной платы для увеличения соответствующего напряжения, показанного на рисунке 22.

На рисунке 23 показана схема Оценочной комиссии.

Заключение

В этом руководстве мы реализовали восьмиканальный измеритель максимального (или минимального) напряжения, который будет использоваться как обычное дополнение к многоканальным системам управления. Представленный подход использует расширенные возможности компонентов GreenPAK и показывает, как можно объединить в одном чипе аналоговые и цифровые функции. Некоторые коммерческие ИС можно заменить на Dialog GreenPAK, чтобы уменьшить размер приложения и снизить стоимость.

Рекомендуемые:

Монитор напряжения для высоковольтных батарей: 3 шага (с изображениями)

Монитор напряжения для высоковольтных батарей: в этом руководстве я объясню вам, как я построил свой монитор напряжения батареи для моей электрической лонгборда. Установите его как хотите и подключите к батарее всего два провода (Gnd и Vcc). В этом руководстве предполагается, что напряжение вашей батареи превышает 30 вольт, w

Понижающий преобразователь напряжения постоянного тока в понижающий режим понижающего напряжения (LM2576 / LM2596): 4 ступени

Понижающий преобразователь напряжения постоянного и понижающего режима понижающего напряжения (LM2576 / LM2596): создание высокоэффективного понижающего преобразователя - сложная работа, и даже опытным инженерам требуется несколько конструкций, чтобы найти правильный. представляет собой преобразователь постоянного тока в постоянный, который понижает напряжение (при повышении

Rainmeter - Настройка минимального рабочего стола (Win 10): 30 шагов

Rainmeter - Настройка минимального рабочего стола (Win 10): Спасибо, что посмотрели это руководство! Это руководство поможет вам создать минимальный рабочий стол с некоторыми полезными виджетами, которые помогут вам очистить рабочий стол от беспорядка. Помните, что это руководство предназначено для Windows 10

Настольный аналоговый источник питания DIY с прецизионным ограничителем тока: 8 шагов (с изображениями)

Настольный аналоговый источник питания DIY с прецизионным ограничителем тока: в этом проекте я покажу вам, как использовать знаменитый LM317T с силовым транзистором усилителя тока и как использовать усилитель считывания тока Linear Technology LT6106 для прецизионного ограничителя тока. использовать до более 5А

Аналоговый термометр Arduino DIY: 7 шагов (с изображениями)

Аналоговый термометр Arduino DIY: Дорогие друзья, добро пожаловать в другой урок! Сегодня мы узнаем, как использовать этот аналоговый вольтметр с Arduino и заставить его показывать температуру вместо напряжения. Как видите, в этом модифицированном вольтметре мы можем видеть температуру в де