Оглавление:

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 11:49.

- Последнее изменение 2025-01-23 15:04.

Автор AmCoder https://www.linkedin.com/in/mituFollow Еще от автора:

О себе: Миту Радж - просто хобби и ученик - дизайнер микросхем - разработчик программного обеспечения - энтузиаст физики и математики Подробнее об AmCoder »

## Это наиболее посещаемая и популярная ссылка в Google для VHDL-реализации CORDIC ALGORITHM для генерации синусоидальной и косинусоидальной волны. ## В настоящее время существует множество эффективных аппаратных алгоритмов, но они малоизвестны из-за преобладания программных систем над много лет. CORDIC - это такой алгоритм, который представляет собой не что иное, как набор логики сдвига и добавления, используемый для вычисления широкого спектра функций, включая определенные тригонометрические, гиперболические, линейные и логарифмические функции. Это алгоритм, используемый в калькуляторах и т. Д. Таким образом, просто используя простые шифтеры и сумматоры, мы можем спроектировать аппаратное обеспечение с меньшей сложностью, но мощностью DSP, используя сердечный алгоритм. Следовательно, он может быть разработан как простой RTL-дизайн на VHDL или Verilog без использования каких-либо выделенных модулей с плавающей запятой или сложных математических IP-адресов.

Шаг 1: VHDL и Modelsim

Здесь сердечный алгоритм реализован с использованием VHDL для генерации синусоидальной и косой волны. Он может выводить синус и косинус входного угла с большой точностью. Код можно синтезировать на ПЛИС. Modelsim используется для моделирования конструкции и испытательного стенда.

Шаг 2: код VHDL для проектирования и испытательный стенд

Для представления чисел с плавающей запятой используется метод двоичного масштабирования.

Пожалуйста, ознакомьтесь с прилагаемой документацией, прежде чем писать код.

Пройдите через Моделирование cordic_v4.vhd - Дизайн -Ввод - угол в 32 бита + бит знака; он может обрабатывать любой угол от 0 до +/- 360 градусов с точностью ввода 0,000000000233 градуса. При вводе -> MSB является битом знака, а остальные 32 бита представляют величину. -Выходом схемы является его значение синуса и cos в 16 битах + бит знака.ie; с точностью 0,00001526. Обратите внимание, что результат отображается в форме дополнения 2, если соответствующее значение синуса или cos отрицательное. Моделирование testb.vhd - Испытательный стенд для проекта (1) Введите углы и сбросьте значение = '0'. После двух шагов симуляции сбросьте на «1» и «запустить все». (2) В окне симуляции установите систему счисления sin и cos сигналов как десятичную и формат> Аналоговый (автоматически). (3) Уменьшите масштаб, чтобы увидеть форму сигнала должным образом.

Шаг 3: прикрепленные файлы

(1) cordic_v4.vhd - Дизайн. (2) testb.vhd - Тестовый стенд для дизайна.

(3) Документируйте, как принудительно вводить угловые значения и преобразовывать двоичные результаты.

Обновление: ЭТИ ФАЙЛЫ УСТАРЕЛИ И БОЛЬШЕ НЕ ПРЕДОСТАВЛЯЮТСЯ. ПОЖАЛУЙСТА, ИСПОЛЬЗУЙТЕ ФАЙЛЫ СО СЛЕДУЮЩЕГО ШАГА

Шаг 4: IP-ядро Mini-Cordic - 16 бит

Ограничение вышеупомянутой реализации - медленная, более низкая тактовая частота работы из-за выполнения вычислений за один тактовый цикл. Mini-Cordic IP Core - 16 бит

- Критические пути распределены по нескольким циклам для повышения производительности. - Быстрее - Проверенная конструкция FPGA синтезирует тактовую частоту до 100 МГц. - Большая область оптимизирована для HDL, меньшее оборудование. - Добавлены сигналы состояния загрузки и завершения. - Единственным недостатком является меньшее разрешение по сравнению с предыдущий.

полностью автоматизированный ввод углов от 0 до 360 градусов

Прикрепленные файлы: 1) основной файл vhdl mini cordic 2) испытательный стенд mini cordic 3) руководство по Mini Cordic IP Core 4) документ о том, как форсировать углы и преобразовывать результаты

По любым вопросам обращайтесь ко мне:

Миту Радж

следуй за мной:

почта: iammituraj@gmail.com

### Всего загрузок: 325 по состоянию на 01-05-2021 ###

### Код последний раз редактировался: июль-07-2020 ###

Рекомендуемые:

Самобалансирующийся робот - алгоритм ПИД-регулирования: 3 шага

Самобалансирующийся робот - алгоритм ПИД-регулирования: этот проект был задуман, потому что мне было интересно узнать больше об алгоритмах управления и о том, как эффективно реализовать функциональные контуры ПИД-регулирования. Проект все еще находится в стадии разработки, так как модуль Bluetooth еще не добавлен, что позволит

Настольная игра Искусственный интеллект: алгоритм минимакса: 8 шагов

Настольная игра Искусственный интеллект: алгоритм Minimax: Вы когда-нибудь задумывались, как сделаны компьютеры, с которыми вы играете в шахматы или шашки? Не ищите ничего, кроме этого руководства, поскольку оно покажет вам, как создать простой, но эффективный искусственный интеллект (ИИ) с использованием алгоритма Minimax! Используя th

Базовый секундомер с использованием VHDL и Basys3 Board: 9 шагов

Базовый секундомер с использованием VHDL и платы Basys3: добро пожаловать в руководство о том, как создать секундомер с использованием базовой платы VHDL и Basys 3. Мы рады поделиться с вами нашим проектом! Это был последний проект курса CPE 133 (Цифровой дизайн) в Калифорнийском Поли, SLO осенью 2016 года. Проект, который мы создали

Крестики-нолики на Arduino с AI (алгоритм Minimax): 3 шага

Крестики-нолики на Arduino с AI (алгоритм Minimax): в этой инструкции я собираюсь показать вам, как создать игру Tic Tac Toe с AI, используя Arduino. Вы можете играть против Arduino или смотреть, как Arduino играет против самого себя. Я использую алгоритм под названием «минимаксный алгоритм»

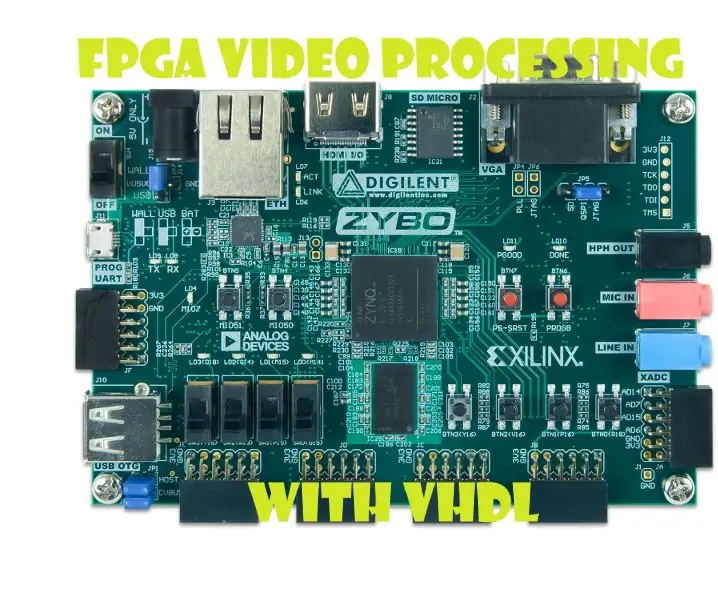

Обработка видео с использованием VHDL и Zybo: 10 шагов

Обработка видео с использованием VHDL и Zybo: FPGA обрабатываются быстрее, чем процессоры, потому что они могут выполнять множество параллельных вычислений. Примечание. Этот проект все еще находится в стадии разработки и будет улучшен (как только у меня появится время). Между тем я путешествую по миру