Оглавление:

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 11:48.

- Последнее изменение 2025-01-23 15:04.

JDM - популярный программатор PIC, потому что он использует последовательный порт, минимум компонентов и не требует источника питания. Но есть путаница, из-за множества вариантов программистов в сети, какие из них работают с какими PIC? В этом «руководстве» мы протестируем JDM, и я продемонстрирую, как смоделировать схему с помощью Spice, которая ответит на все ваши вопросы!

Запасы

LTspice, который можно загрузить с Analog Devices здесь.

Здесь вам также понадобятся файлы схемы JDM.

Шаг 1. Требования к последовательному порту

Для JDM требуется последовательный порт, соответствующий спецификации EIA232, в идеале с уровнями напряжения + 12 / -12.

Согласно спецификации Texas Instruments Line Driver MC1488 (рисунок 3)

Выходное сопротивление = 4 В / 8 мА = 500 Ом.

Предел тока короткого замыкания = 12 мВ, без ограничения по времени - без повреждения микросхемы.

Входное сопротивление линейного приемника = рекомендуется от 3 кОм до 7 кОм.

Последовательные порты на старых настольных ПК используют напряжение +12 В / -12 В, отвечающее этому требованию.

Последовательные порты на новых портативных компьютерах используют более низкое напряжение. JDM может работать, а может и не работать - ответ более сложный.

Шаг 2: Требования к программированию PIC

Информация о требованиях к программированию PIC получена от Microchip. Вышесказанное относится к типичному устройству.

Шаг 3: Спецификация JDM

Неужели оригинальный веб-сайт JDM потерялся в глубине веков? Это заставляет нас догадываться, что дизайнер изначально планировал для спецификации.

- Обеспечьте VDD = 5 В и максимум до IDD = 2 мА (для версии «в розетке»)

- Обеспечьте VHH = 13 В и максимум до IHH = 0,2 мА.

- MCLR Время нарастания tVHHR = 1 мкс макс.

- Версия ICSP должна иметь возможность снижать уровень MCLR до 22 тыс. Подтягиваний на цели.

Шаг 4: Описание схемы

Рисунок JDM1 основан на «стандартной» схеме JDM, взятой с веб-сайта PICPgm. Это программатор «PIC in Socket», в котором PIC получает питание от контактов TX и RTS. Первоначальную диаграмму было трудно понять, поэтому я перерисовал ее, используя обычное соглашение о текущем потоке сверху вниз. И я добавил светодиодные индикаторы «RESET», «PROG» и «RTS», которые необходимы во время строительства и тестирования. Надеюсь, это не окажет вредного воздействия на поведение.

Обычно при проектировании схем все заземления объединены, но ключевой особенностью JDM является то, что земля последовательного порта (GND) подключена к VDD. Это создает путаницу, поскольку сигналы последовательного порта измеряются относительно заземления, сигналы PIC относительно логической земли (VSS).

Когда TX становится высоким, Q1 ведет себя как два диода с прямым смещением. (Коллектор Q1 не имеет обратного смещения, как при нормальной работе транзистора). Коллектор Q1 заряжает C2, который фиксируется стабилитроном (D3) на VDD + 8V. Излучатель Q1 подает 13 В на MCLR для режима программирования / проверки.

Когда TX становится низким, конденсатор C3 заряжается через D1, а VSS фиксируется на VDD-5V стабилитроном (D5). Также TX ограничен (VSS-0.6) D1. Q1 выключен, C1 сохраняет заряд для следующего программного импульса. MCLR фиксируется на 0 В на D2, поэтому теперь PIC находится в состоянии сброса.

Когда RTS высокий, часы передаются на PGC. D4 зафиксируйте PGC при высоком логическом уровне VDD. Когда RTS низкий, конденсатор C3 заряжается через D6, а VSS фиксируется на VDD-5V стабилитроном (D5). D6 фиксирует PGC на VSS или логическом 0.

Во время программирования данные, отправленные на DTR, считываются на PGD, который PIC конфигурирует как вход. Когда DTR высокий, Q2 действует как «эмиттерный повторитель», а напряжение PGD составляет примерно (VDD-0,6) или логическую 1. Когда DTR низкий, Q2 действует как неисправный транзистор (контакты эмиттера и коллектора переставлены). Q2 подтягивает PGD к низкому уровню, который фиксируется D7 на VSS или логическом 0.

Во время проверки PIC настраивает PGD как выход для отправки данных на последовательный порт. DTR должен быть установлен на высокий уровень, и данные читаются на CTS. Когда выход PGD высокий, Q2 выключен, CTS = DTR = + 12V. Когда выход PGD низкий, Q2 включен. Коллектор Q2 потребляет ток (12 В + 5 В) / (1 к + 1 к 5) = 7 мА от DTR и понижает CTS до VSS.

Шаг 5: Подготовка к моделированию

Загрузите LT spice, сохраните и откройте файлы схемы (*.asc), представленные здесь. Чтобы смоделировать схему, мы должны дать ей некоторые входные данные, а затем «проследить» выходы. V1, V2 V3 моделируют последовательный порт 12 В с выходным сопротивлением R11, R12, R13.

- V1 генерирует 2 программных импульса на TX от 0,5 мс до 4,5 мс

- V2 генерирует пакет импульсов данных на DTR от 1,5 до 4,5 мс.

- V3 генерирует пакет тактовых импульсов на RTS от 0,5 до 3,5 мс.

Компоненты V4, X1, R15 и R16 являются частью моделирования.

- V4 генерирует 2 импульса от 2,5 до 4,5 мс для проверки данных.

- Перемычка X1 имитирует ВЫХОД на PGD.

- R15, R16 имитируют «загрузку» PIC на VDD и MCLR.

Шаг 6: Модификации для ICSP

На рисунке JDM3 показана версия для программирования «в схеме». Изменения от оригинала есть

- Замените разъем ZIF на разъем ICSP.

- Теперь PIC получает питание от целевой цепи (V5).

- Снимите стабилитрон 5 В (D5).

- Маленький конденсатор 100 пФ (C4) перемещается рядом с PIC на целевой цепи.

- Светодиоды получают питание от печатной платы, где это возможно.

- В целевой цепи требуются подтягивающий резистор (R10) и диод (D10) MCLR.

- ПРЕДУПРЕЖДЕНИЕ. Целевая плата должна иметь «плавающий» источник питания, в идеале - аккумулятор.

- Не подключайте целевое заземление (VSS) к заземлению компьютера / ПК, подключая любые другие порты компьютера одновременно с JDM.

После моделирования JDM1 проблема длительного времени зарядки на C2 стала очевидной. Затем после прочтения Фруттенбуля выясняется, что C2 и Q1 были добавлены как модификация оригинала. Я не могу понять, для чего предназначены C2 и Q1, кроме создания проблем. Поэтому для JDM4 мы возвращаемся к старому дизайну Fruttenboel, который прост и понятен. D1 и D3 / LED2 зажимают MCLR между VSS и VDD + 8V. Значение R1 уменьшено до 3k3, чего достаточно, чтобы зажечь LED2 при напряжении 12 В.

JDM4 также предназначен для работы с более слабыми последовательными портами. Когда TX становится высоким (+ 9V), источник тока TX = (9-8) / (1k + 3k3) = 0,2 мА, достаточно, чтобы поднять MCLR на высокий уровень, хотя и недостаточно для включения LED2. Когда TX становится низким (около -7V), потребление тока TX = (9-7) / 1k = 2 мА. Ток светодиода 1 = (7-2 для светодиода) / (2k7) = 1,8 мА. Ток понижения MCLR = 7-5,5 / 3k3 = 0,5 мА.

Эта схема также была протестирована (моделирование JDM5), чтобы увидеть, что происходит с последовательными портами минимум +/- 7 В, где недостаточно напряжения для поддержания VHH = 13 В. Назначение C1 теперь становится очевидным: C1 создает кратковременный положительный импульс для MCLR, импульс 33 мкс на переднем фронте TX, достаточно длинный, чтобы PIC мог войти в режим программирования, возможно? Но снимите перемычку X2 (отключите LED1), поскольку недостаточно тока, чтобы сбросить MCLR на низкий уровень и одновременно зажечь LED1. Когда TX становится низким, потребление тока TX = (7V-5.5V) / (1k + 3k3) = 0.3mA, чего достаточно, чтобы подтянуть MCLR к низкому уровню против подтягивающего R10.

Шаг 7: Результаты моделирования

Для просмотра графических файлов лучше щелкнуть правой кнопкой мыши по ссылкам ниже, а затем выбрать «Открыть ссылку в новой вкладке».

Моделирование 1: трассировка MCLR, VSS и RTS для исходного JDM1. Сразу становятся очевидными наблюдения 1, 2 и 3.

Моделирование 2: трассировка MCLR и VSS, а также RTS для модифицированного JDM2, который устраняет предыдущие проблемы.

Моделирование 3: трассировка PGD, VSS и PGC для передачи данных JDM2 в программном режиме. Наблюдение 4 на 3,5 мс.

Моделирование 4: трассировка PGD, VSS и CTS для JDM2 в режиме проверки (перемычка X1 вставлена). Ok

Моделирование 5: трассировка MCLR, VSS, PGD и PGC для JDM3. ICSP, использующий питание от схемы, решает множество проблем.

Моделирование 6: трассировка MCLR, VSS, PGD и PGC для JDM4 с последовательным портом +/- 9 В. MCLR поднимается сразу, полностью рабочий.

Моделирование 7: трассировка MCLR, VSS и TX для JDM5 с последовательным портом +/- 7 В и удаленной перемычкой X2. C1 создает положительное усиление (всплеск) на нарастающем фронте MCLR, которого примерно достаточно, чтобы подтолкнуть MCLR выше TX до 13 В.

Шаг 8: выводы

Spice действительно хорошо раскрывает «скрытые секреты» работы схем. Очевидно, схема JDM работает и совместима со многими микросхемами PIC, но следующие наблюдения показывают возможные ограничения / проблемы / сбои совместимости?

- Большое время нарастания MCLR, пока C2 заряжается до VPP в первом импульсе TX. Не соответствует спецификации 3.

- Последовательный порт заряжает C2, когда TX становится высоким, а RTS становится низким. Но RTS также заряжает C3. Когда оба происходят одновременно, это создает большую нагрузку на RTS, следовательно, C3 теряет заряд (VSS повышается) через 2 мс при моделировании. Не соответствует спецификации 1.

- C3 теряет заряд (VSS начинает расти) после остановки тактовых импульсов на 3,5 мс.

- Для чего нужен С2, он вообще нужен?

Решения

- Предположительно, PICPgm использует программный «обходной цикл». Он должен подать длинный импульс TX для предварительной зарядки на C2, а затем войти в режим программирования только после второго импульса TX? Для моделирования я уменьшил значение C2 до 1 мкФ, чтобы время нарастания составляло 1 мс. Не идеальное решение.

- Разделите C2 и C3, чтобы они заряжались независимо. Одна небольшая модификация JDM2, C2 ссылается на GND вместо VSS.

- Решено JDM3. ICSP намного надежнее, поскольку PIC питается от целевой цепи.

- JDM4 решает проблему 1. Это простая конструкция, полностью исключающая C2.

Шаг 9: И наконец

Доказательство того, что пудинг - это еда. Этот JDM работает, так что продолжайте его использовать.

И мои рекомендации:

- используйте JDM2 для программирования сокетов и последовательных портов 12 В,

- используйте JDM4 для программатора ICSP и последовательных портов выше +/- 9 В,

- используйте JDM4 с удаленной перемычкой X2 для последовательных портов с напряжением выше +/- 7 В.

Использованная литература:

Analog Devices LT специя

picpgm

Fruttenboel

Следите за другими проектами PIC на сайте Sly-Corner

Рекомендуемые:

KS-Garden: Обзор: 9 шагов

KS-Garden: Обзор: KS-Garden можно использовать для орошения / вентиляции / освещения вашего сада / тепличных растений на заднем дворе или ваших комнатных растений для выращивания растений (модульная конструкция) Система KS-Garden состоит в основном из следующих модулей: системный блок - Реле и блок питания

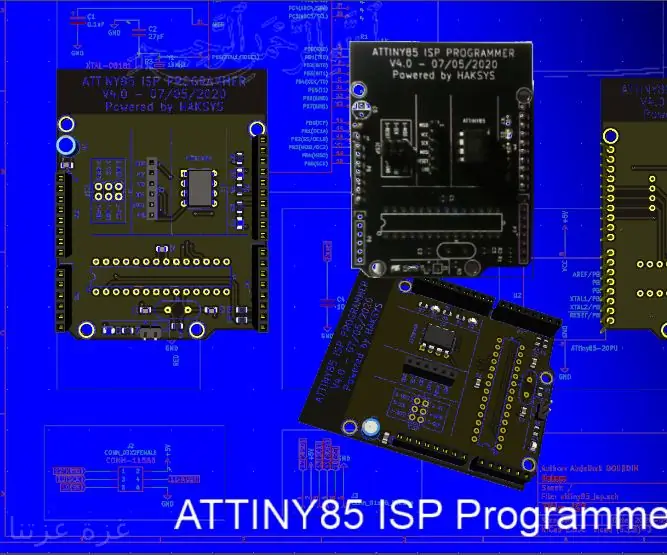

Еще один щит программиста ISP ATTINY85 для Arduino: 8 шагов

Еще один ATTINY85 ISP Programmer Shield для Arduino: الله الرحمن الرحيم ATTINY85 ISP Programmer Shield предназначен для простого программирования микроконтроллеров ATTiny85. Экран должен быть подключен к плате Arduino Uno. Последовательный программист & quot

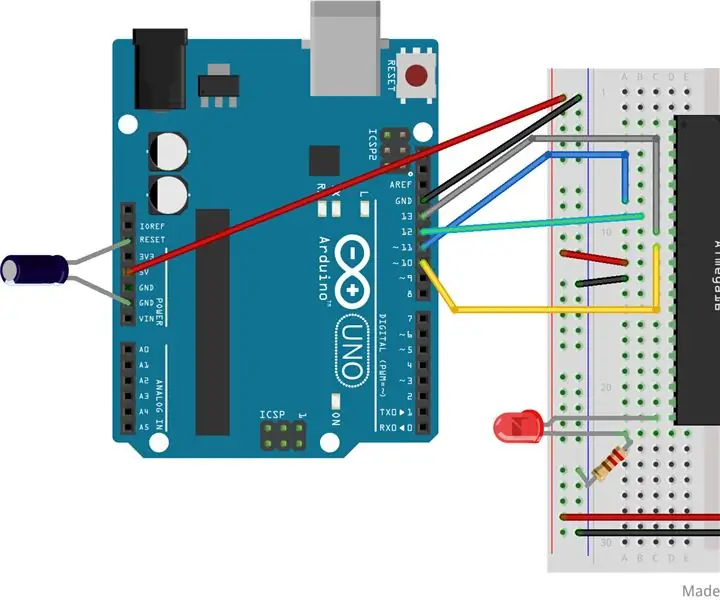

Как загрузить код C в AVR с помощью Arduino Uno в качестве программиста: 6 шагов

Как загрузить код C в ِ AVR с помощью Arduino Uno в качестве программиста: Привет всем: D Здесь я расскажу о простом способе программирования любого чипа AVR с помощью Arduino Uno R3. программист, который дорого стоит

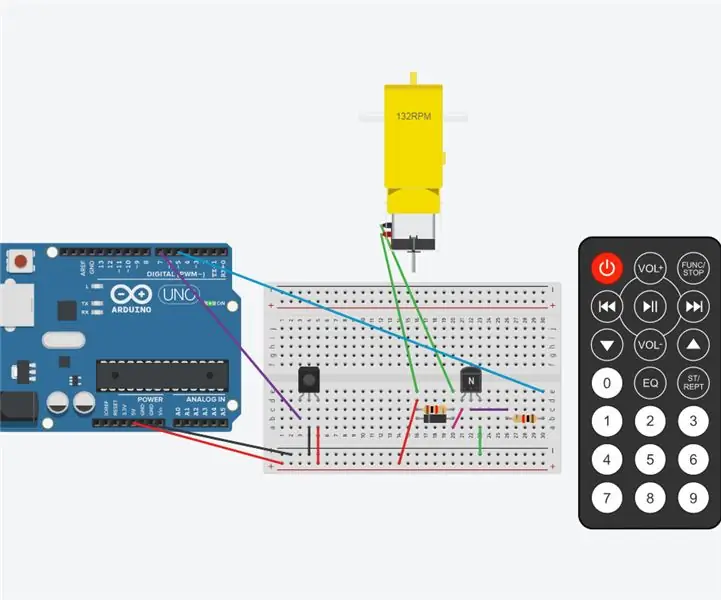

Двигатель с транзисторным управлением и дистанционным управлением; обзор схемы: 9 шагов

Двигатель с транзисторным управлением и дистанционным управлением; Обзор схемы: Эта схема представляет собой двигатель с транзисторным управлением и дистанционным управлением. Дистанционное управление включает питание. Транзистор включает двигатель. Код программы увеличит скорость двигателя и затем уменьшите скорость двигателя до нуля

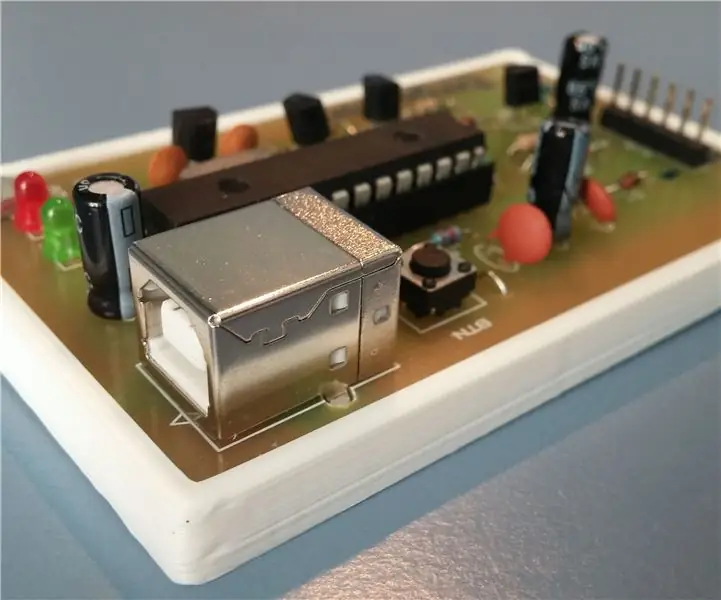

Как сделать PIC-программиста - «клон» PicKit 2: 4 шага (с изображениями)

Как сделать PIC-программиста - «клон» PicKit 2: Привет! Это краткое руководство по созданию программатора PIC, который действует как PicKit 2. Я сделал это, потому что это намного дешевле, чем покупка оригинального PicKit, и потому что Microchip, производители микроконтроллеров PIC и программатор PicKit, пр