Оглавление:

- Шаг 1. Создание модуля PWM - исходный файл

- Шаг 2: Создание модуля ШИМ - настройка Vivado

- Шаг 3. Создание модуля PWM - создание файла проекта

- Шаг 4: Создание модуля ШИМ - конструкция блока и настройка файла ограничений (I)

- Шаг 5: Создание модуля ШИМ - конструкция блока и настройка файла ограничений (II)

- Шаг 6: Создание модуля ШИМ - конструкция блока и настройка файла ограничений (III)

- Шаг 7: Создание модуля ШИМ - конструкция блока и настройка файла ограничений (IV)

- Шаг 8: Создание модуля ШИМ - конструкция блока и настройка файла ограничений (V)

- Шаг 9: Сборка модуля ШИМ - установка оборудования

- Шаг 10: Создание модуля PWM - создание битового потока и запуск SDK

- Шаг 11: Создание модуля PWM - создание нового приложения в Xilinx SDK

- Шаг 12: Создание модуля PWM - Обзор Project Explorer (I)

- Шаг 13: Создание модуля PWM - Обзор Project Explorer (II)

- Шаг 14: Создание модуля PWM - Обзор Project Explorer (III)

- Шаг 15: Создание модуля ШИМ - завершение функции ШИМ (I)

- Шаг 16: Создание модуля ШИМ - завершение функции ШИМ (II)

- Шаг 17: Создание модуля ШИМ - завершение функции ШИМ (III)

- Шаг 18: Создание модуля ШИМ - заставить его работать

- Шаг 19: Обработка потокового видео на Digilent ZYBO с OV7670

- Шаг 20: Полная блок-схема

- Шаг 21: Подключите OV7670 к ZYBO

- Шаг 22: Создание блочного дизайна

- Шаг 23. Добавьте файлы VHDL для управления камерой OV7670 и захвата

- Шаг 24: Добавьте файл ограничений

- Шаг 25: Добавьте IP-репозиторий для HLS IP

- Шаг 26: Добавьте модули и IP

- Шаг 27: Параметры конфигурации IP

- Шаг 28: Добавьте и настройте блок IP PS

- Шаг 29: Часть 1. Создание модуля ШИМ для серводвигателей

- Шаг 30: Соединения со стороны видеовхода (выделено значком)

- Шаг 31: Подключения к OV7670

- Шаг 32: Подключения на стороне видеовыхода

- Шаг 33: Запустите автоматизацию блокировки и подключения

- Шаг 34: Создайте оболочку HDL

- Шаг 35: создание битового потока, экспорт оборудования в SDK, запуск SDK из Vivado

- Шаг 36: SDK (без FreeRTOS)

- Шаг 37: Внедрение FreeRTOS

- Шаг 38: Инструкции по использованию

- Шаг 39: ссылки и ссылки

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 11:53.

- Последнее изменение 2025-01-23 15:05.

Начните с первого шага, чтобы получить подробную информацию о создании 2-осевого серво ШИМ-контроллера.

Начните с массивной блок-схемы (шаг 19) для всего проекта.

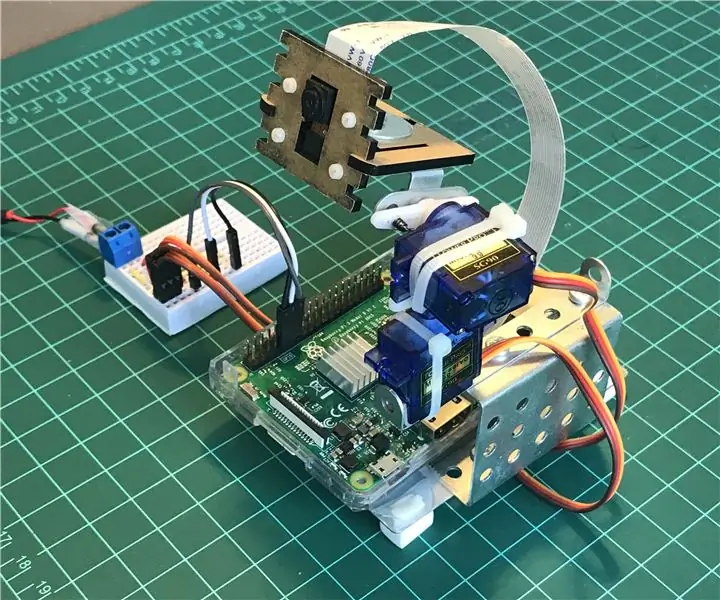

Используемая нами настройка камеры + панорамирования / наклона:

PmodCON3 от Digilent использовался для подключения сервоприводов.

Шаг 1. Создание модуля PWM - исходный файл

Шаг 2: Создание модуля ШИМ - настройка Vivado

Сначала загрузите Vivado Design Suite с веб-сайта Xilinx. Установите весь пакет для проектирования, включая Vivado Software Development Kit (SDK). В этом проекте используется версия 2017.2.

Тем временем Digilent Adept 2 также должен быть установлен как драйвер платы Zybo.

Шаг 3. Создание модуля PWM - создание файла проекта

Перед созданием файла проекта вы должны убедиться, что вы уже правильно установили файл Zybo, как показано здесь:

Установка файла платы Vivado версии 2015.1 и более поздних версий

Откройте Vivado 2017. 2. В разделе «Быстрый старт» нажмите «Создать проект» -> «Далее» -> «Имя проекта» (укажите здесь название проекта) -> «Тип проекта». В разделе «Тип проекта» выберите «Проект RTL» и отметьте «Не указывать источники в настоящее время». Затем для партии по умолчанию выберите «Платы» и «Zybo» в качестве отображаемого имени. Затем нажмите «Готово», чтобы запустить проект.

Шаг 4: Создание модуля ШИМ - конструкция блока и настройка файла ограничений (I)

В Flow Navigator нажмите «Create Block Design», затем нажмите OK. щелкните значок «+», чтобы добавить необходимые IP-адреса. Добавлять:

- Одна система обработки ZYNQ7 Два таймера AXI

- Два таймера AXI

Шаг 5: Создание модуля ШИМ - конструкция блока и настройка файла ограничений (II)

После добавления IP запустите автоматизацию блоков и автоматизацию подключения. После завершения автоматизации в блоке «axi_timer_0» щелкните правой кнопкой мыши на pwm0 -> Сделать внешним. Назовите внешний вывод pwm0 как pwm_Xaxis. Кроме того, повторите описанный выше процесс для блока «axi_timer_1» и назовите внешний вывод pwm0 как pwm_Zaxis.

Шаг 6: Создание модуля ШИМ - конструкция блока и настройка файла ограничений (III)

Обратите внимание, что каждый раз, когда мы заканчиваем дизайн блока в Vivado, нам нужно создать HDL Wrapper. Поскольку это будет модуль верхнего уровня для каждого проекта.

Шаг 7: Создание модуля ШИМ - конструкция блока и настройка файла ограничений (IV)

Теперь нам нужно настроить наш файл ограничений для назначения выводов, подключенных к нашей блок-диаграмме. Закройте окно «Дизайн блока», на вкладке «Источники», «Добавить источники» -> Добавить или создать ограничения-> добавить Zybo-Master.xdc в качестве наших файлов ограничений.

Шаг 8: Создание модуля ШИМ - конструкция блока и настройка файла ограничений (V)

Откройте файл ограничений Zybo-Master.xdc из папки Constraints, раскомментируйте порты, которые мы хотим указать в качестве выходных сигналов, и переименуйте «get_ports {XXXX}», где XXXX обозначает внешний вывод, названный в блок-схеме. Настройка файла ограничений показана на рисунке.

Шаг 9: Сборка модуля ШИМ - установка оборудования

Подключите серводвигатели к Pmod CON3. TowerPro SG90 - это модель серводвигателя, которую мы использовали в этом проекте. Для проводов серводвигателя оранжевый провод представляет собой сигнал ШИМ, подключенный к выводу SIG в Pmod CON3. Красный провод Vcc - это провод питания, подключенный к выводу VS в Pmod CON3. Наконец, коричневый провод Gnd - это провод заземления, подключенный к контакту GND. Затем вставьте Pmod CON3 в верхний ряд порта JD на плате Zybo.

Шаг 10: Создание модуля PWM - создание битового потока и запуск SDK

1. На вкладке Project Navigator запустите Generate BitStream.

2. Экспортируйте оборудование: Файл> Экспорт> Экспорт оборудования-> отметьте «включить битовый поток» -> OK 3. Запустите SDK: Файл -> Запустить SDK.

Шаг 11: Создание модуля PWM - создание нового приложения в Xilinx SDK

Создайте новое приложение:

Файл> Создать> Проект приложения -> Введите имя вашего проекта -> Готово

В Project Explorer должно быть три папки.

В этом случае «design_1_wrapper_hw_platform_0» - это папка, ранее экспортированная Vivado. Axis_2_PWM_SDK_bsp - это папка пакета поддержки платы. Axis_2_PWM_SDK - это наша основная папка проекта в SDK. Вы можете увидеть файл «helloworld.c» в папке «src» Axis_2_PWM_SDK, где «helloworld.c» - это главный файл.

Шаг 12: Создание модуля PWM - Обзор Project Explorer (I)

Давайте проверим несколько файлов в Project Explorer. Сначала в папке «design_1_wrapper_hw_platform_0» откройте «system.hdf». Этот файл демонстрирует карту адресов для процессора ps7_cortex9 и IP-блоков, присутствующих в нашем проекте.

Шаг 13: Создание модуля PWM - Обзор Project Explorer (II)

Затем проверьте файлы include и libsrc в папке Axis_2_PWM_SDK_bsp. Файлы библиотеки здесь позволяют нам взаимодействовать с аппаратной периферией без «игровых» регистров.

Шаг 14: Создание модуля PWM - Обзор Project Explorer (III)

В документации BSP xtmrctr.h находится как библиотека управления таймером Xilinx, связанная с таймером AXI. Обычно мы могли найти здесь желаемую функцию ШИМ. Однако, если вы читаете документацию «tmrctr_v4_3», она показывает, что драйвер в настоящее время не поддерживает работу устройства с ШИМ. Из-за недостатка функции PWM мы должны завершить нашу функцию PWM с помощью xtmrctr.h и AXI Timer v2.0 LogiCORE IP Product Guide.

Шаг 15: Создание модуля ШИМ - завершение функции ШИМ (I)

Вернитесь к основному файлу helloworld.c и включите следующие файлы заголовков:

Шаг 16: Создание модуля ШИМ - завершение функции ШИМ (II)

Определите базовые адреса двух AXI TImer через «xparameters.h».

Шаг 17: Создание модуля ШИМ - завершение функции ШИМ (III)

Создайте желаемую функцию ШИМ.

Duty_val: преобразует значение градуса в рабочий цикл PWM_Freq_Duty: устанавливает желаемую частоту и рабочий цикл для генерации ШИМ. Также следует указать период времени.

PWM_START: назначьте адрес регистра ШИМ и начните генерировать ШИМ.

PWM_STOP: назначить адрес регистра ШИМ и прекратить генерацию ШИМ.

Остальной демонстрационный код показан в «helloworld.c» в разделе «Axis_2_PWM_SDK».

Шаг 18: Создание модуля ШИМ - заставить его работать

1. Программируем ПЛИС через SDK

- Подключите Zybo Board через USB-порт к ПК.

- Xilinx Tools -> Программирование FPGA

2. запустить программу

Щелкните значок «Выполнить» и выпадающее меню -> Запуск от имени -> Запуск на оборудовании

3. SDK Терминал

- Откройте терминал SDK -> Подключиться к последовательному порту -> ОК

- Запустите программу. Если демонстрационный код работает успешно, вы должны увидеть «Инициализация выполнена!» на SDK Terminal.

Шаг 19: Обработка потокового видео на Digilent ZYBO с OV7670

Полный архивный файл прилагается.

Шаг 20: Полная блок-схема

Это показывает полную схему всех подключений и IP-блоков в проекте.

Шаг 21: Подключите OV7670 к ZYBO

Создайте соединение для подключения модуля ov7670 к модулям ZYBO Pmods.

Data Pmod - это Pmod D

Control Pmod - это Pmod C

Кроме того, подключите PmodCON3 и сервоприводы, как указано в первой половине этого руководства.

Шаг 22: Создание блочного дизайна

В Flow Navigator нажмите «Create Block Design», затем нажмите OK.

Шаг 23. Добавьте файлы VHDL для управления камерой OV7670 и захвата

Добавьте файлы VHDL, прикрепленные к этому шагу, в проект.

Шаг 24: Добавьте файл ограничений

Добавьте прикрепленный файл ограничений в свой проект.

Шаг 25: Добавьте IP-репозиторий для HLS IP

Возьмите прикрепленный Zip-файл и разархивируйте его в новую папку с аналогичным названием в новом каталоге (папке) под названием «HLS_repo».

Добавьте репозиторий IP в свой проект, перейдя в каталог IP и щелкнув правой кнопкой мыши, выбрав «Добавить репозиторий…»

Перейдите в свой каталог «HLS_repo» и выберите его.

Необязательно: Создайте для себя блок обработки видео HLS!

Шаг 26: Добавьте модули и IP

Добавьте модули ov7670_axi_stream_capture, debounce и ov7670_controller на блок-диаграмму, щелкнув фон правой кнопкой мыши и выбрав «Добавить модуль…»

Точно так же добавьте IP-адреса:

- HLS_Video_Track

- Запись буфера кадра видео

- Чтение буфера кадра видео

- Видео контроллер времени

- AXI4-поток на видеовыход

- 3 из «Срезов»

- Постоянный

- 2 таймера AXI

Шаг 27: Параметры конфигурации IP

Как показано на фотографиях

Шаг 28: Добавьте и настройте блок IP PS

Добавьте систему обработки ZYNQ7 на блок-схему

отредактируйте конфигурацию:

-

Конфигурация PS-PL

-

HP

- Включить S HP 0

- Включить S HP 1

-

-

Конфигурация часов

-

PL тканевые часы

- FCLK_0 на 100 МГц

- FCLK_1 на 25 МГц (OutputClock)

- FLCK_2 на 35 МГц (<= 50 МГц) (CameraClock)

-

Шаг 29: Часть 1. Создание модуля ШИМ для серводвигателей

Вывести axi_timer_0 pwm0 на новый выходной порт pwm_Xaxis

Вывести axi_timer_1 pwm0 на новый выходной порт pwm_Zaxis

Шаг 30: Соединения со стороны видеовхода (выделено значком)

Правильно подключите IP-блоки со стороны видеовхода

(* эти соединения должны быть созданы путем выбора правильных опций во время автоматизации соединения) "aclk" из axi_stream_capture переходит к:

- ap_clk при записи буфера кадра видео

- ap_clk в блоке обработки видеопотока HLS

- * aclk на AXI smartconnect IP из буфера кадра видео Запись в S_AXI_HP0

- * aclk, соответствующий каналам IP-адреса AXI Interconnect для каналов S_AXI блока обработки видео HLS, и буфер видеокадров записывает S_AXI_HP0_ACLK в блоке PS

Сигнал видеопотока просто подключается последовательно от блока захвата к интерфейсу памяти Zynq.

- Видео переходит из блока захвата в блок обработки HLS.

- Обработанное видео из блока HLS поступает в блок записи кадрового буфера.

- * Блок записи кадрового буфера подключается к интерфейсу HP0 на блоке Zynq PS.

- Сигнал m_axis_tuser с выхода блока захвата вручную подключается как к входному сигналу video_in_TUSER в блоке обработки HLS, так и к сигналу ap_start в том же блоке.

Сигнал TUSER (tuser) используется протоколом видеопотока AXI для обозначения начала кадра видео. AP_Start сообщает блоку HLS начать обработку. Таким образом, мы используем tuser для запуска блока HLS для обработки каждого кадра по мере его выполнения. входит. При подключении отдельного сигнала шины и его разделении таким образом необходимо также подключить его к нормальной оконечной точке остальной шины. Vivado предполагает, что если вы подключаете сигнал вручную, вы хотите отключить то, к чему он обычно подключается.

Параметры конфигурации IP-блоков:

Запись буфера кадра видео:

Форматы видео: RGB8

1 выборка за такт Максимальное количество столбцов: 1280 (> = 640) Максимальное количество строк: 960 (> = 480) Максимальная ширина данных: 8

Шаг 31: Подключения к OV7670

На блоке ov7670_axi_stream_capture

- Сделайте все входы внешними (щелкните правой кнопкой мыши на булавке и выберите из меню, или щелкните левой кнопкой мыши-> ctrl + T)

- Оставьте имена такими, какие они есть

На блоке ov7670_controller

- Сделайте все выходы блока внешними

- Переименуйте порт config_finished в led0

- подключите clk к CameraClock (<= 50MHz) (FCLK_2)

На блоке устранения дребезга

- подключите вход button1 к внешнему входному порту с именем btn0

- подключите out1 к линии повторной отправки на IP-блоке ov7670_controller

- подключите вход button2 к внешнему входному порту с именем btn3

- подключите out2n к входу ext_reset_in на IP-адресе сброса системы процессора для домена тактовой частоты видеозахвата. (* Это может потребоваться после того, как этот IP-адрес будет сгенерирован *)

- подключите clk к CameraClock (<= 50MHz) (FCLK_2)

Шаг 32: Подключения на стороне видеовыхода

Соединения для блоков Video Timing Controller (VTC), AXI4-Stream to Video Out и слайсов

- Используйте частоту 25 МГц (FCLK_1) для vid_io_out_clk и VTC clk

- Используйте тактовую частоту 100 МГц (FCLK_0) для ACK на AXI4-Stream to Video Out

- vtiming_out в vtiming_in

- Буфер кадра видео Чтение m_axis_video переходит в AXI4-Stream в Video Out video_in

- vtg_ce переходит к gen_clken

- Свяжите VTC clken, aclken, vid_io_out_ce с постоянным dout [0: 0]

- Выведите vid_hsync и vid_vsync на внешние выходные порты vga_hs и vga_vs соответственно. (без изображения)

Ломтики:

-

Срезы должны быть настроены, как показано на прилагаемых рисунках.

- переименуйте блоки в slice_red, slice_green и slice_blue

- настройте диапазоны срезов, как показано на изображениях, по названию блока

- подключите каждый выход среза к выходу внешнего порта, как показано на рисунке.

- vid_data [23: 0] подключается к входам для каждого среза (Din [23: 0])

Шаг 33: Запустите автоматизацию блокировки и подключения

Запустите Block Automation, чтобы подключить вещи из блока ZYNQ7 PS. Как показано на картинке.

Запустите автоматизацию подключений, чтобы создать все IP-адреса подключения. Обратите особое внимание на все варианты на каждой картинке.

На блоке устранения дребезга подключите out2n к входу ext_reset_in в области тактовой частоты видеозахвата.

Шаг 34: Создайте оболочку HDL

Сгенерируйте HDL Wrapper для вашего блочного дизайна.

Установите его как верхний модуль.

Шаг 35: создание битового потока, экспорт оборудования в SDK, запуск SDK из Vivado

Не забудьте включить битовый поток в экспорт.

Генерация битового потока может занять очень много времени.

Затем запустите SDK

Шаг 36: SDK (без FreeRTOS)

Эта версия делает все без использования FreeRTOS, красиво уплотняя код.

Создайте автономный BSP на основе конструкции оборудования. Параметры по умолчанию должны быть в порядке. Убедитесь, что источники BSP созданы.

Создайте приложение, как показано на рисунке. (пустое приложение)

Удалите автоматически созданный основной файл и импортируйте прикрепленные файлы.

Шаг 37: Внедрение FreeRTOS

Эта версия действительно использует FreeRTOS. Создайте FreeRTOS901 BSP на основе конструкции оборудования. Параметры по умолчанию должны быть в порядке. Убедитесь, что источники BSP созданы.

Создайте приложение, как показано на рисунке. (пустое приложение)

Удалите автоматически созданный основной файл и импортируйте прикрепленные файлы.

Шаг 38: Инструкции по использованию

Этот проект немного сложно запустить. Следуйте инструкциям по порядку.

Убедитесь, что ваш ZYBO ничего не загружает самостоятельно при включении. Это означает, что светодиод «Готово» не должен гореть. Один из способов сделать это - установить перемычку источника загрузки в положение JTAG.

Откройте проект (FreeRTOS или нет), который вы хотите запрограммировать из SDK

- Включите ваш ZYBO. Светодиод «Готово» не должен гореть.

- Запрограммируйте FPGA с битовым файлом. Светодиод Done должен загореться. Led0 не должен загореться.

- Запустите код (не забудьте пропустить начальную точку останова, если вы это делаете).

На этом этапе вы должны получить вывод на свой VGA-дисплей.

Чтобы перезапустить (в случае ошибки или чего-то еще): быстро нажмите кнопку PS-SRST или выключите ZYBO, а затем снова включите. Продолжайте с шага 2.

Остановка процессора с помощью отладчика приведет к тому, что камера будет удерживать позицию, а не двигаться. Видеопоток все равно будет продолжен.

Шаг 39: ссылки и ссылки

Справочные руководства и документация Xilinx:

- PG044 - AXI-поток на видеовыход

- PG278 - чтение / запись буфера кадра видео

Другие ссылки:

- Блог Лаури - ввод VDMA

- Блог Лаури - OV7670 в вывод VGA с использованием BRAM

- Hamsterworks wiki, автор - Майк Филдс, первоисточник кода OV7670.

- Технический паспорт с указанием основных временных характеристик

Рекомендуемые:

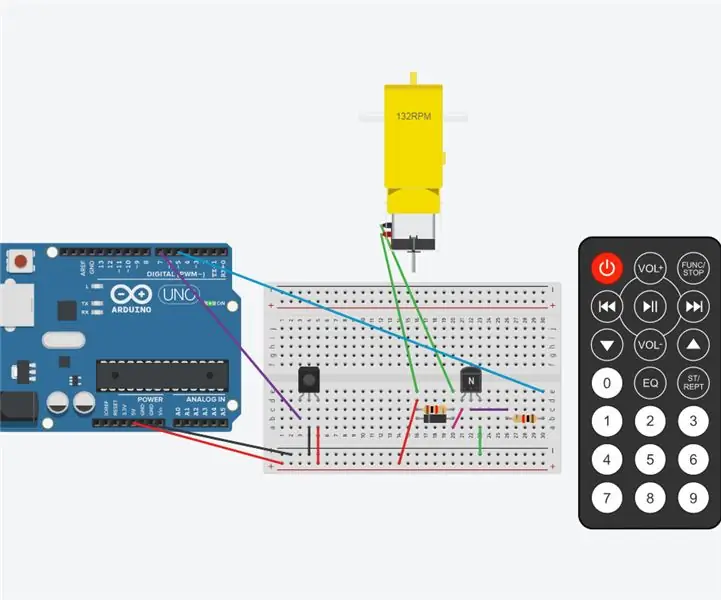

Двигатель с транзисторным управлением и дистанционным управлением; обзор схемы: 9 шагов

Двигатель с транзисторным управлением и дистанционным управлением; Обзор схемы: Эта схема представляет собой двигатель с транзисторным управлением и дистанционным управлением. Дистанционное управление включает питание. Транзистор включает двигатель. Код программы увеличит скорость двигателя и затем уменьшите скорость двигателя до нуля

Робот Arduino с голосовым управлением + камера Wi-Fi + захват + приложение, ручное использование и режим обхода препятствий (KureBas Ver 2.0): 4 шага

Робот Arduino с голосовым управлением + камера Wi-Fi + захват + приложение и ручное использование и режим предотвращения препятствий (KureBas Ver 2.0): вернулся KUREBAS V2.0 Он очень впечатляет новыми функциями. У него есть захват, камера Wi-Fi и новое приложение, созданное для него

Мульти сервоуправление панорамированием и наклоном: 11 шагов (с изображениями)

Управление несколькими сервоприводами панорамирования-наклона: в этом руководстве мы рассмотрим, как управлять несколькими сервоприводами с помощью Python на Raspberry Pi. Нашей целью будет механизм PAN / TILT для позиционирования камеры (PiCam). Здесь вы можете увидеть, как будет работать наш окончательный проект: Control Servo Control loop test:

Камера с управлением движением с использованием MESH SDK: 6 шагов (с изображениями)

Камера с контролем движения с использованием MESH SDK: Хотите автоматизировать камеру, чтобы снимать лучшие моменты вашего питомца, пока вас нет дома? Датчик движения MESH делает возможным использование камер, поддерживающих SDK. Например, мы разместили датчик движения MESH рядом с кормом для кошек и игрушками для кошек, чтобы c

Объектив камеры DSLR с наклоном и сдвигом DIY: 6 шагов

Объективы для зеркальных фотокамер с наклоном и сдвигом своими руками: Что вам понадобится: 1) SLR или корпус камеры DSLR со сменным объективом. 2) Увеличенный объектив. Ebay - отличный ресурс, вы можете подобрать высококачественный объектив примерно за $ 15,3. Резиновый аккордеонный поршень (желательно черный, чтобы предотвратить попадание света