Оглавление:

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 11:51.

- Последнее изменение 2025-01-23 15:05.

Я поражен тем, какие ответы я получаю в этом блоге. Спасибо, ребята, что посетили мой блог и побудили меня поделиться с вами своими знаниями. На этот раз я собираюсь представить дизайн еще одного интересного модуля, который мы видим во всех SOC - Контроллер прерываний.

Мы будем проектировать простой, но мощный программируемый контроллер прерываний. Это полностью настраиваемый и параметризованный дизайн, который можно переносить на разные платформы. Я разработал это после того, как много читал о некоторых популярных архитектурах контроллеров прерываний, таких как NVIC, 8259a, RISC-V PLIC, Microblaze's INTC и т. Д. Надеюсь, вы, ребята, найдете этот блог полезным и поможет вам понять, как прерывания обрабатываются процессором. с помощью контроллера прерываний.

Шаг 1: Технические характеристики

Ниже приведены характеристики IP:

- Интерфейс AHB3-Lite.

-

Статически настраиваемые параметры:

- Кол-во внешних источников прерываний; поддерживает до 63 прерываний.

- Количество уровней приоритета; поддерживает до 63 уровней.

- Количество уровней вложенности; поддерживает до 8 уровней вложенности.

- Ширина автобуса; 32 или 64.

- Глобально и локально маскируемые прерывания.

- Динамически настраиваемый уровень приоритета для каждого прерывания.

- Два режима работы - полностью вложенный режим и режим равного приоритета.

- Поддерживает прерывания, чувствительные к активному высокому уровню.

В конструкции использован механизм квитирования прерывания, основанный на спецификациях RISC-V PLIC.

Упреждение прерывания основано на 8259a

Прочие чтения: Microblaze INTC, NVIC

Шаг 2: Обзор PIC

Программируемый контроллер прерываний (PIC) получает несколько прерываний от внешних периферийных устройств и объединяет их в один выход прерывания для ядра целевого процессора.

PIC контролируется через регистры управления и состояния. Все регистры PIC отображены в память и доступны через интерфейс шины AHB3-Lite.

Банк регистров состоит из регистра конфигурации, регистров разрешения, регистров ожидания, регистров обслуживания, регистров приоритета и регистра идентификатора, которые типичны для контроллеров прерываний.

Регистр конфигурации используется для установки режима работы PIC. Он может работать как в полностью вложенном режиме, так и в режиме равного приоритета.

Каждому прерыванию можно назначить приоритеты и индивидуально замаскировать. Также поддерживается глобальное маскирование всех прерываний.

Банк регистров взаимодействует с Priority Resolver и BTC (Binary-Tree-Comparator), чтобы определить приоритеты ожидающих прерываний и соответственно заявить прерывание процессору. Регистр ID содержит ID ожидающего прерывания с наивысшим приоритетом.

Шаг 3: Разработка и реализация RTL

При проектировании PIC упор делается на уменьшение задержки решения приоритетов, что является наиболее критичной по времени частью проекта. Поскольку проект решает приоритеты за один тактовый цикл, производительность ухудшается с увеличением количества источников со сложностью Log2.

Дизайн был успешно реализован, и синхронизация проверена до следующих частот на ПЛИС Artix-7.

- До 15 источников: 100 МГц

- До 63 источников: 50 МГц

Задержка прерывания, добавляемая только PIC, составляет 3 тактовых цикла (исключая время переключения контекста процессора и время выборки первой инструкции ISR).

Шаг 4: важные примечания и прикрепленные файлы

Важные заметки:

- Если интерфейс AHB3-Lite нежелателен, вы можете изменить верхний модуль и использовать каркасный дизайн PIC. Однако предоставленный тестовый стенд предназначен для IP с интерфейсом AHB3-Lite.

- PIC IP v1.0 - это полностью переносимый, чистый RTL-дизайн.

- Функционально проверено для работы в обоих режимах.

Прикрепленные файлы:

- Коды проектирования и тестовая среда на VHDL.

- Полная документация по IP.

Это проект с открытым исходным кодом … Не стесняйтесь использовать …

По любым вопросам, в любое время:

Миту Радж

Рекомендуемые:

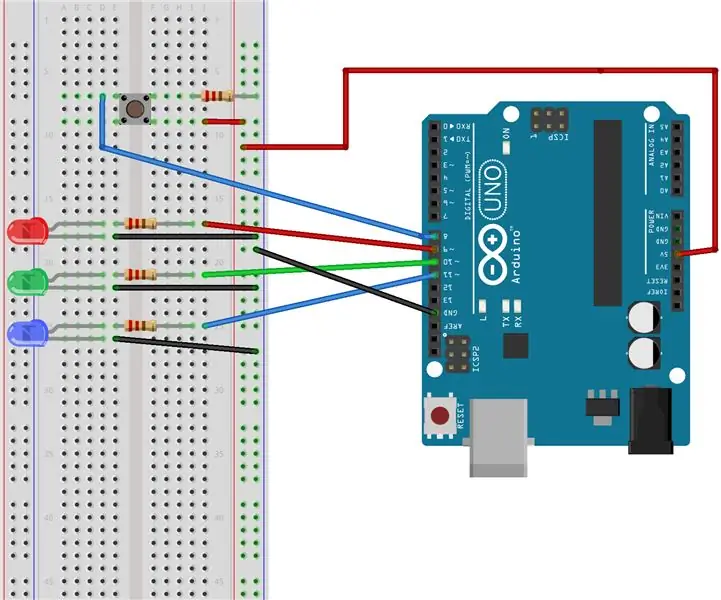

Лаборатория прерываний (работа в процессе): 3 шага

Лаборатория прерываний (работа в процессе): цель этой лабораторной работы - запустить программу Arduino с использованием прерываний. Эта лабораторная работа работает некорректно из-за проблем с кодированием. Что вам понадобится: - 1 Arduino Uno - 1 макетная плата - 1 кнопка - 3 светодиода - резисторы 220 Ом - перемычки

Разработка простого четырехкомпонентного ассоциативного контроллера кэширования на VHDL: 4 шага

Проектирование простого четырехстороннего ассоциативного контроллера кэширования на VHDL. В моем предыдущем руководстве мы увидели, как разработать простой контроллер кэш-памяти с прямым отображением. На этот раз мы идем на шаг впереди. Мы будем проектировать простой четырехсторонний ассоциативный контроллер кеш-памяти. Преимущество ? Меньше промахов, но за счет перфорации

Разработка простого контроллера кеша на VHDL: 4 шага

Проектирование простого контроллера кеша на VHDL: я пишу это руководство, потому что мне было немного сложно получить некоторый эталонный код VHDL для изучения и начала проектирования контроллера кеша. Поэтому я сам разработал контроллер кеш-памяти с нуля и успешно протестировал его на ПЛИС. У меня п

Разработка простого контроллера VGA на VHDL и Verilog: 5 шагов

Проектирование простого контроллера VGA на VHDL и Verilog: в этом руководстве мы собираемся разработать простой контроллер VGA на RTL. Контроллер VGA - это цифровая схема, предназначенная для управления дисплеями VGA. Он считывает из буфера кадра (память VGA), который представляет кадр, который нужно отобразить, и генерирует необходимые

Микроконтроллер AVR. Светодиоды мигают с использованием таймера. Таймеры прерываний. Режим таймера CTC: 6 шагов

Микроконтроллер AVR. Светодиоды мигают с использованием таймера. Таймеры прерываний. Timer CTC Mode: Всем привет! Таймеры - важная концепция в области электроники. Каждый электронный компонент работает по расписанию. Эта временная шкала помогает синхронизировать всю работу. Все микроконтроллеры работают на определенной тактовой частоте